# AN14249

# Migration Guide from LPC55xx to MCX Nx4x

Rev. 1 — 2 April 2024

**Application note**

#### **Document information**

| Information | Content                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14249, migration guide                                                                                                                    |

| Abstract    | This document provides an overview of the differences between the LPC55xx and MCX Nx4x chips and helps to migrate from LPC55xx to MCX Nx4x. |

Migration Guide from LPC55xx to MCX Nx4x

# 1 Introduction

This document provides an overview of the differences between the LPC55xx and MCX Nx4x chips and helps to migrate from LPC55xx to MCX Nx4x. The migration between these chips requires the software changes. This document describes the changes require to migrate from LPC55xx to MCX Nx4x. LPC553x, LPC556x, and MCX Nx4x are used as the examples in this document.

# 2 Chip comparison

This section compares the main features between the LPC553x, LPC556x, and MCX Nx4x chips.

#### 2.1 MCX Nx4x series overview

The MCX Nx4x chip is based on the Arm Dual Cortex-M33 core and operates at the speed of up to 150 MHz and provide for industrial and consumer IoT applications. It has three features:

- Highly secure: TrustZone for Armv8-M, secure boot/update ROM, and the NXP EdgeLock secure subsystem

(ELS) S50 black-box secure enclave with key storage and crypto algorithms protected from side-channel

attacks as well as internal/external tamper events, flash encryption, external memory interface with on-thefly PRINCE decryption, options for hardware Physically Unclonable Function (PUF) and Factory Root of Trust

programming.

- Industrial Strength: Industrial communication protocol support, 15-year longevity, high-resolution mixed signal analog, CAN-FD, BLDC/PMSM Motor Control support, integrated sensor interfaces (MIPI-I3C, I<sup>2</sup>C, SPI).

- Power-efficient:

- < 75 μA/MHz active current,

- < 10 µA power-down mode with RTC enabled and 8 kB SRAM retention,

- < 2.5 μA Deep power-down mode with RTC active and 8 kB SRAM.

#### 2.2 LPC55xx series overview

All LPC55Sxx/LPC55xx families are based on Arm Cortex-M33 core, with PowerQuad accelerator and CASPER accelerator. The **S** in the middle of part name means that this part provides more security features, such as TrustZone support.

- Power-efficient:

- < 82 μA/MHz active current,

- < 8 μA Power-down mode with RTC enabled and 8 kB SRAM retention

- < 2.5  $\mu$ A Deep power-down mode with RTC active and 4 kB SRAM

# 2.3 High-level comparison

Table 1. High-level comparison of MCX Nx4x and LPC55xx

| Features          |                 | LPC55S69 | LPC55S36 | MCX N947 |

|-------------------|-----------------|----------|----------|----------|

| CPU core platform | M33 @150 MHz    | 2        | 1        | 2        |

|                   | PowerQuad (DSP) | YES      | YES      | YES      |

| Co-processor      | Smart DMA       | _        | _        | YES      |

|                   | NPU             | _        | _        | YES      |

AN14249

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved

# Migration Guide from LPC55xx to MCX Nx4x

Table 1. High-level comparison of MCX Nx4x and LPC55xx...continued

| Features                |                                     | LPC55S69                                              | LPC55S36                                                    | MCX N947                                                     |

|-------------------------|-------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|

|                         | CoolFlux DSP                        | _                                                     | _                                                           | YES                                                          |

|                         | CASPER                              | YES                                                   | _                                                           | _                                                            |

|                         | Flash                               | 640 kB                                                | 256 kB                                                      | 2 MB, Dual bank                                              |

|                         | Flash cache                         | _                                                     | 8 kB                                                        | 16 kB                                                        |

|                         | SRAM                                | 320 kB                                                | Up to 112 kB, no<br>ECC                                     | Up to 480 kB, no ECC                                         |

| Memory                  | SRAM ECC                            | _                                                     | 16 kB                                                       | 32 kB                                                        |

|                         | FlexSPI                             | _                                                     | YES, with <b>8 kB</b> cache, supporting XIP, Octal/Quad SPI | YES, with <b>16 kB</b> cache, supporting XIP, Octal/Quad SPI |

|                         | ROM                                 | YES                                                   | YES                                                         | YES                                                          |

|                         | EdgeLock                            |                                                       | _                                                           | EdgeLock 50 B                                                |

| Security                | Secure key management               | PUF                                                   | PUF/UDF                                                     | PUF/UDF                                                      |

| Security                | Secure subsystem                    | _                                                     | YES                                                         | YES                                                          |

|                         | Anti-tamper pin                     | _                                                     | 4 × Pins                                                    | 8 × Pins                                                     |

| General system          | DMA                                 | 2 × (22<br>channels/10<br>channels)                   | 2 × DMA (52<br>channels/16<br>channels)                     | 2 × DMA/16<br>channels each                                  |

|                         | CRC                                 | YES                                                   | YES                                                         | YES                                                          |

|                         | FRO-1 MHz                           | YES                                                   | YES                                                         | _                                                            |

|                         | FRO-12 MHz                          | _                                                     | _                                                           | YES                                                          |

|                         | FRO-96/12 MHz                       | YES                                                   | YES                                                         | _                                                            |

|                         | FRO-144 MHz                         | _                                                     | _                                                           | YES                                                          |

|                         | FRO-16 kHz                          | _                                                     | _                                                           | YES                                                          |

| Clocking                | FRO-32 kHz                          | YES                                                   | Yes                                                         | _                                                            |

|                         | 32 kHz low-power crystal oscillator | YES, with cap-<br>bank                                | YES, with cap-<br>bank                                      | YES, with cap-<br>bank                                       |

|                         | External crystal oscillator         | 16 MHz to 32 MHz,<br>with cap-bank                    | 16 MHz to 32 MHz, with cap-bank                             | 16 MHz to 50 MHz<br>low-power crystal<br>oscillator          |

|                         | PLL                                 | 2 ×                                                   | 2 ×                                                         | 2 ×                                                          |

|                         | USART                               | 40 v Flaveau                                          | 0 v Flores                                                  | 10 × LP Flexcomm,                                            |

|                         | SPI                                 | 10 × Flexcomm, each supporting                        | 8 × Flexcomm, each supporting                               | each supporting                                              |

|                         | I <sup>2</sup> C                    | SPI, I <sup>2</sup> C, USART,<br>and I <sup>2</sup> S | SPI, I <sup>2</sup> C,USART, and I <sup>2</sup> S           | SPI, I <sup>2</sup> C, UART                                  |

| Communication Interface | I <sup>2</sup> S/SAI                | and i 3                                               |                                                             | 2 × SAI                                                      |

|                         | HighSpeed SPI                       | 1 × 50 MHz                                            | 1 × 50 MHz                                                  | _                                                            |

|                         | I <sup>3</sup> C                    | _                                                     | 1 ×                                                         | 2 ×                                                          |

|                         | eSPI                                | _                                                     | _                                                           | 1 ×                                                          |

# Migration Guide from LPC55xx to MCX Nx4x

Table 1. High-level comparison of MCX Nx4x and LPC55xx...continued

| Features                |                           | LPC55S69                                            | LPC55S36                                     | MCX N947                                      |

|-------------------------|---------------------------|-----------------------------------------------------|----------------------------------------------|-----------------------------------------------|

|                         | SPI Filter                | _                                                   | 1 ×                                          | YES                                           |

|                         | FlexIO                    | _                                                   | _                                            | 1 ×                                           |

|                         | EVM smart card            | _                                                   | _                                            | 2 ×                                           |

|                         | CAN-FD                    | _                                                   | 1 ×                                          | 2 ×                                           |

|                         | HighSpeed USB             | 1 × Device/Host                                     | _                                            | 1 × Device/Host                               |

|                         | Full Speed USB            | 1 × Device/Host                                     | 1 × Device with<br>Crystal-less              | 1 × Device/Host                               |

|                         | uSDHC                     | 1 ×                                                 | _                                            | 1 ×                                           |

|                         | Ethernet                  | _                                                   | _                                            | 1 ×                                           |

|                         |                           |                                                     | 4 × single-ended input 16-bit 2.0 Msps       | 4 × single-ended input 16-bit 2.0Msps         |

|                         | ADC                       | 1 × 16-bit ADC<br>with 1.0 Msps,<br>supporting five | 2 × differential<br>input 16-bit 2.0<br>Msps | 2 × differential<br>input 16-bit 2.0<br>Msps  |

|                         | ADC                       | differential inputs<br>or 10 single-ended<br>inputs | 4 × single-ended input 12-bit 3.2 Msps       | 4 × single-ended input 12-bit 3.16 Msps       |

| Analog                  |                           |                                                     | 2 × differential<br>input 12-bit 3.2<br>Msps | 2 × differential<br>input 12-bit 3.16<br>Msps |

|                         | DAC                       | _                                                   | 3 × 12-bit DAC 1<br>Msps                     | 2 × 12-bit 1 Msps 1<br>× 14-bit 5 Msps        |

|                         | Comparator                | 1 × with 5 inputs                                   | _                                            | _                                             |

|                         | High-speed comparator     | _                                                   | 3 ×                                          | 3 × High Speed,<br>with 17 inputs             |

|                         | Opamp                     | _                                                   | 4 ×                                          | 3 ×                                           |

|                         | Accurate V <sub>ref</sub> | _                                                   | _                                            | YES                                           |

|                         | FlexPWM                   | _                                                   | 2 × FlexPWM (4<br>submodule for<br>each)     | 2 × FlexPWM (4<br>submodule for<br>each)      |

|                         | ENC/QEI/QDC               | _                                                   | 2 × QEI                                      | 2 × ENC                                       |

| Motor control subsystem | Event generator           | _                                                   | _                                            | 1 × (including two AOI)                       |

|                         | AOI                       | _                                                   | 2 ×                                          | _                                             |

|                         | SINC filter               | _                                                   | _                                            | YES (third order, 5-ch)                       |

|                         | CTimer                    | 5 × 32-bit                                          | 5 × 32-bit                                   | 5 × 32-bit                                    |

| Timers                  | SCTimer/PWM               | 1 × 32-bit or 2 × 16-bit                            | 1 × 32-bit or 2 × 16-bit                     | 1 × 32-bit or 2 × 16-bit                      |

|                         | LPTimer                   | _                                                   | -                                            | 1 ×                                           |

|                         | Encoder                   | _                                                   | _                                            | 1 ×                                           |

# Migration Guide from LPC55xx to MCX Nx4x

Table 1. High-level comparison of MCX Nx4x and LPC55xx...continued

| Features          |                                            | LPC55S69                                          | LPC55S36                                              | MCX N947                                                                        |

|-------------------|--------------------------------------------|---------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------|

|                   | Frequency measurement timer                | 1 ×                                               | 1 ×                                                   | 1 ×                                                                             |

|                   | Multi-Rate Timer (MRT)                     | 4 ×                                               | 4 ×                                                   | 1 ×                                                                             |

|                   | Windowed Watchdog timer                    | 1 ×                                               | 1 ×                                                   | 1 ×                                                                             |

|                   | RTC                                        | RTC without calendar                              | RTC with calendar                                     | RTC with calendar                                                               |

|                   | Micro Timer                                | 1 ×                                               | 1 ×                                                   | 1 ×                                                                             |

|                   | OS Event Timer                             | 1 ×                                               | 1 ×                                                   | 1 ×                                                                             |

|                   | Digital PDM Microphone                     | No                                                | 1 ch - Allows<br>connection of up to<br>2 × MEMS      | Supporting the connection of up to four MEMS                                    |

| НМІ               | Capacitive Touch Sensor<br>Interface (TSI) | No                                                | No                                                    | Up to 25 self-<br>channels, and<br>up to 8 TX × 17<br>RX mutual-cap<br>channels |

|                   | GPIO                                       | 64 GPIOs on<br>HLQFP100<br>36 GPIOs on<br>HTQFP64 | 66 GPIOs on<br>HLQFP100<br>39 GPIOs on<br>HTQFP64     | Up to 124 × GPIOs<br>on VFBGA184, 100<br>MHz IO on P2 and<br>P3                 |

|                   | Internal Core Buck DC-DC                   | YES                                               | YES, 1.8 V to 3.6 V                                   | YES                                                                             |

|                   | Internal Core LDO                          | No                                                | YES, 1.8 V to 3.6 V                                   | YES                                                                             |

|                   | Always On Domain on VDD_VBAT pin           | No                                                | YES, 1.71 V to 3.6<br>V                               | YES                                                                             |

|                   | Operating Voltage                          | 1.8 V to 3.6 V                                    | 1.8 V to 3.6 V                                        | 1.71 V to 3.6 V                                                                 |

| Operation Details | IOs                                        | 1.8 V to 3.6 V                                    | VDDIO_1 is 1.8 V - 3.6 V. VDDIO_2 is 1.08 V to 3.6 V. | 1.71 V to 3.6 V at full-performance 1.2 V supporting at reduced performance     |

|                   | VHBM                                       | ± 2000 V                                          | ± 2000 V                                              | +-± 2000 V                                                                      |

|                   | VCDM                                       | ± 500 V                                           | ± 500 V                                               | ± 500 V                                                                         |

|                   | VFBGA184                                   | _                                                 | _                                                     | YES                                                                             |

|                   | HLQFP100                                   | YES                                               | YES                                                   | YES                                                                             |

| Package           | VFBGA98                                    | YES                                               | _                                                     | _                                                                               |

|                   | HTQFP64                                    | YES                                               | YES                                                   | _                                                                               |

|                   | HVQFN48                                    | _                                                 | YES                                                   | _                                                                               |

Migration Guide from LPC55xx to MCX Nx4x

# 3 System modules comparison

### 3.1 Memory system difference

### 3.1.1 Memory system on LPC55xx

Table 2. Memory system on LPC55xx

| Memory type    | Start address | Size         | MCU          | Comment                 |

|----------------|---------------|--------------|--------------|-------------------------|

| Internal Flash | 0x0000 0000   | Up to 640 kB | All LPC55xx  | _                       |

| SRAM           | 0x2000 0000   | Up to 272 kB | All LPC55xx  | SRAM on CM33 data bus   |

| SRAM X         | 0x0400 0000   | Up to 32 kB  | All LPC55xx  | SRAM X on CM33 code bus |

| FlexSPI        | 0x0800 0000   | Up to 128 MB | Only LPC553x | _                       |

| Boot ROM       | 0x0300 0000   | Up to 192 kB | All LPC55xx  | On CM33 code bus        |

### 3.1.2 Memory system on MCX Nx4x

Table 3. Memory system on MCX Nx4x

| Memory type    | Start address | Size                            | MCU          | Comment                 |

|----------------|---------------|---------------------------------|--------------|-------------------------|

| Internal Flash | 0x0000 0000   | Up to 2 MB                      | All MCX Nx4x | _                       |

| SRAM           | 0x2000 0000   | Up to 512 kB, including ECC RAM | All MCX Nx4x | SRAM on CM33 data bus   |

| SRAM X         | 0x0400 0000   | 96 kB                           | All MCX Nx4x | SRAM X on CM33 code bus |

| FlexSPI        | 0x0800 0000   | Up to 128 MB                    | All MCX Nx4x | _                       |

| Boot ROM       | 0x0300 0000   | 256 kB                          | All MCX Nx4x | On CM33 code bus        |

# 3.1.3 Memory system comparison

On the MCX Nx4x chips, the memory address is compatible with LPC55xx series.

# 3.2 Clocking differences

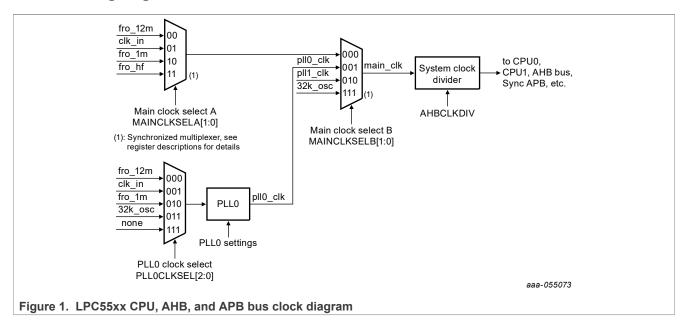

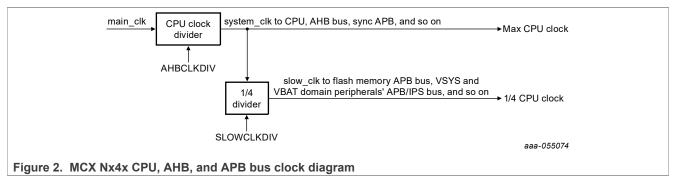

The system clocking module provides the clock signals to the core, memories, and peripherals (register interfaces and peripheral clocks).

#### Migration Guide from LPC55xx to MCX Nx4x

### 3.2.1 Clocking diagram on LPC55xx

### 3.2.2 Clocking diagram on MCX Nx4x

MCX Nx4x series added SLOW clock (1/4 CPU clock) to flash memory, APB bus, and other domain. LPC55xx series do not have this clock.

#### 3.2.3 Clock feature comparison

Table 4. Comparison of MCX Nx4x and LPC55xx clock features

| Feature                | MCX Nx4x                                   | LPC55xx                                     |

|------------------------|--------------------------------------------|---------------------------------------------|

| Maximum core frequency | 150 MHz                                    | 150 MHz                                     |

| PLL                    | 2 × PLL up to 550 MHz                      | 2 × PLL up to 550 MHz                       |

| External oscillator    | 16 MHz to 50 MHz<br>32.768 kHz             | 16 MHz or 32 MHz<br>32.768 kHz              |

| Internal FRO           | FRO: 144 MHz<br>FRO: 12 MHz<br>FRO: 16 kHz | FRO: 96/12 MHz<br>FRO: 1 MHz<br>FRO: 32 kHz |

Migration Guide from LPC55xx to MCX Nx4x

# 4 Peripheral module comparison

# 4.1 Changed modules

#### 4.1.1 SYSCON

The whole SYSCON module is changed, but the functionality remains similar.

### 4.1.2 Internal Flash Memory

The whole Flash module is changed, but the functionality remains similar.

Table 5. Comparison of internal flash

| Feature                                    | Description                                                                                                                                                                                                                       | MCXN                                                             | LPC55xx                                                                                   |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Flash array • Phrase                       | It represents the smallest portion of the flash memory that can be programmed in one operation.                                                                                                                                   | 16 bytes                                                         | The LPC55xx does no have flash phrase, and the LPC55xx minimum program size is 512 bytes. |

| Flash array • Sector                       | It represents the smallest portion of the flash memory that can be erased in one operation.                                                                                                                                       | 8 kB                                                             | The minimum erase size is 512 bytes.                                                      |

| Flash array • Page                         | It represents the largest portion of the flash memory that can be programmed in one operation.                                                                                                                                    | 128 bytes                                                        | 512 bytes                                                                                 |

| Flash memory controller  • Prefetch buffer | It prefetches the next 128-bit flash memory location.                                                                                                                                                                             | 16 bytes                                                         | _                                                                                         |

| Flash memory controller  • Cache           | Flash Cache memory stores already fetched data. This code is immediately available for repeated execution without any wait states, if needed. It is a one set, four-way associative cache with 128-bit (or 16-byte) size entries. | 64 bytes                                                         |                                                                                           |

| Functional safety • Flash ECC              |                                                                                                                                                                                                                                   | One-bit error correction.     Two-bit error detection capability | One-bit error correction                                                                  |

| Functional safety Flash ERM                | ERM provides information and optional interrupt notification on memory ECC and parity error events.                                                                                                                               | Report ECC two- bit error                                        | _                                                                                         |

| Functional safety • Flash EIM              | EIM provides a method for diagnostic coverage of internal memories. It enables you to induce artificial errors on error-checking mechanisms.                                                                                      | One-bit error injection     Two-bit error injection              | _                                                                                         |

| Flash performance  • Access frequency      | Configured by FCTRL[RWSC] or FLASHTIM                                                                                                                                                                                             | 150 MHz/4 = 37.5 MHz; when<br>RWSC = 3                           | 150 MHz, when FLASHTIM     0xB, 12 system clocks flash access time.                       |

#### Migration Guide from LPC55xx to MCX Nx4x

Table 5. Comparison of internal flash...continued

| Feature | Description | MCXN | LPC55xx                                                                                                                                                             |

|---------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |             |      | <ul> <li>100 MHz, when FLASHTIM = 0x7, eight system clocks flash access time.</li> <li>12 MHz, when FLASHTIM = 0x1, two system clocks flash access time.</li> </ul> |

#### 4.1.3 IOCON to PORT comparison

MCX Nx4x uses PORT to replace the IOCON of LPC55xx, but the functionality remains similar.

#### 4.1.4 GPIO

The whole GPIO module is changed, but the functionality remains similar.

The GPIO of MCX Nx4x supports 1.2 V at the reduced performance (available only on Fast pads).

The GPIO of MCX Nx4x supports 1.71 V -~ 3.6 V IO supply range.

LPC553x supports two main IO supplies: VDDIO 1 is 1.8 V to 3.6 V, and VDDIO 2 is 1.08 V to 3.6 V.

LPC556x only supports 1.8 V to 3.6 V.

#### 4.1.5 Real Time Calendar (RTC)

The RTC module is changed, but the functionality remains similar.

#### 4.1.6 Low-power Timer (LPTMR) and WKT

LPC55xx series integrate with WKT, and MCX N series have this LPTMR feature. The LPTMR and WKT functionality remains similar.

You can configure LPTMR to operate as a time counter with an optional pre-scaler, or as a pulse counter with an optional glitch.

Filter, across all power modes, includes low-power modes. It is reset only on VSYS warm reset, allowing it to be used as a time-of-day counter.

#### 4.1.7 I<sup>3</sup>C

The I<sup>3</sup>C module is updated on MCX Nx4x, but the functionality remains similar.

#### 4.1.8 Controller Area Networ (CAN)

LPC556x series do not have CAN module. LPC553x and MCX Nx4x have the CAN module.

The whole CAN module is changed, but the functionality remains similar. Both of them support CAN2.0 and CAN-FD.

#### 4.1.9 Flexcomm and LP Flexcomm

LPC55xx series use Flexcomm linked with USART, SPI, I<sup>2</sup>C, and I<sup>2</sup>S serial peripherals.

MCX Nx4x series use LP\_Flexcomm linked with LPUART, LPSPI, and LPI2C.

The whole UART module is changed, but the functionality remains similar.

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved

#### Migration Guide from LPC55xx to MCX Nx4x

The whole I<sup>2</sup>C module is changed, but the functionality remains similar.

The whole SPI module is changed, but the functionality remains similar. LPSPI on MCX Nx4x supports 4-bit mode where SPI of LPC553x and LPC556x does not support.

# 4.1.10 I<sup>2</sup>S and Serial Audio Interface (SAI)

LPC55xx series use I<sup>2</sup>S interface from Flexcomm to connect audio codec. MCX Nx4x uses the SAI interface connected with audio codec. The I<sup>2</sup>S and SAI functionalities remain similar.

#### 4.1.11 DMIC and MICFIL

LPC553x series use Digital Microphone (DMIC) interface to receive Pulse Density Modulated (PDM) data from multiple digital microphones and process it to produce 24-bit PCM data.

MCX Nx4x uses PDM Microphone Interface (MICFIL) delivers audio from microphones to the processor in several applications, such as mobile telephones. As the current digital audio systems use a multi-bit audio signal (also known as multi-bit PCM) to represent the signal, this module implements the required digital interface (a series of filters) to transform a PDM microphone bitstream into a 24-bit PCM signal in the audio band, at a configurable output sample rate.

Both DMIC and MICFIL functionalities remain similar.

#### 4.1.12 USB

The whole USB module is changed, but the functionality remains similar.

#### 4.1.13 Secure Digital Input Outpu (SDIO)

LPC553x series do not integrate with SDIO.

LPC556x has one SDIO. The whole SDIO module is changed on MCX Nx4x, but the functionality remains similar.

#### 4.1.14 Semaphores2 (SEMA42) and Inter-CPU mailbox

LPC55xx series integrate Inter-CPU mailbox and MCX N series have this SEMA42 feature. The SEMA42 and Inter-CPU mailbox functionality remains similar.

SEMA42 is a memory-mapped module that provides robust hardware support needed in multi-core systems for implementing semaphores and provides a simple mechanism to achieve **lock and unlock** operations via a single-write access. The hardware semaphore module provides hardware-enforced gates and other useful system functions related to the gating mechanisms.

#### 4.1.15 Direct Memory Access (DMA)

The whole DMA module is changed, but the functionality remains similar.

#### 4.2 New modules

#### 4.2.1 Core Mode Controller (CMC)

LPC55xx series do not integrate with CMC, but MCX N series have this feature.

CMC provides the sequencing of the CPU and associated logic through the different operating modes.

AN14249

Migration Guide from LPC55xx to MCX Nx4x

#### 4.2.2 Interrupt Monitor (INTM)

LPC55xx series do not integrate with INTM, but MCX N series have this feature.

INTM provides a mechanism to monitor the latency of the responses on interrupt requests to ensure that the processing of these critical interrupts executes within the expected time frame, increasing the reliability of the device.

#### 4.2.3 Error Injection Module (EIM)

LPC55xx series do not integrate with EIM, but MCX N series have this feature.

EIM is used for diagnostic purposes. It provides a method for diagnostic coverage of internal memories (for example, system RAM, cache RAMs, and peripheral memories). To determine which functional safety features that this method supports, see the chip-specific EIM information.

EIM enables you to induce artificial errors on error-checking mechanisms of a system, such as ECC for RAM read data and parity bits. For each mechanism that EIM supports on the chip, EIM can inject single-bit and multi-bit inversions on data in the applicable target bus. Injecting faults on memory accesses can be used to exercise the SEC-DED ECC function of the related system.

### 4.2.4 Error Recording Module (ERM)

LPC55xx series do not integrate with ERM, but MCX N series have this feature.

ERM provides information and optional interrupt notification on memory error events associated with ECC and parity. ERM collects error events on memory accesses for memory arrays, such as flash memory, system RAM, or peripheral RAMs. ERM supports various channels for memory sources where each ERM channel is associated with a different memory module. See the chip-specific ERM information for details about supported memory sources and specific memory channel assignments. If the memory supports ECC, then ERM syndrome and error address information are captured along with the error event. ERM does not capture syndrome or error address for cache memories or memory with parity instead of ECC.

#### 4.2.5 Event Generator (EVTG) and AOI

LPC556x does not have this feature. LPC553x series integrate with AOI. MCX N series integrate with EVTG.

EVTG includes two parts:

- Two AND/OR/INVERT (known as the AOI) modules.

- One configurable flip-flop

It supports the generation of a configurable number of Event signals. The two AOI combinational expressions share the four associated EVTG inputs: An, Bn, Cn, and Dn. You can configure the flip-flop to make the two expressions act as the Reset port, Set port or D port, CLK port or go through to EVTG output with the flip-flop bypassed.

This module is a slave peripheral module-connecting event input indicators from various chip modules and generates event output signals that you can route to an inter-peripheral crossbar switch or other peripherals. You can access its programming model through the standard IPS (sky blue) slave interface. EVTG is configurable in the integrated AOI functionality and flip-flop variety.

#### 4.2.6 Neural Processing Unit (NPU)

LPC55xx series do not integrate with NPU, but MCX N series have this feature.

NPU is dedicated for accelerate machine learning algorithms.

AN14249

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

#### Migration Guide from LPC55xx to MCX Nx4x

NPU is a configurable architecture comprising three aspects:

- · Weight decoding

- · Compute engine

- Data canvas

#### 4.2.7 External Watchdog Monitor (EWM)

LPC55xx series do not integrate with EWM, but MCX N series have this feature.

For safety purposes, a redundant watchdog system, EWM, is designed to monitor external circuits and the MCU software flow. This provides a backup mechanism to the internal watchdog that resets the CPU and peripherals of the MCU.

The internal watchdog is used to monitor the flow and execution of the embedded software within the MCU. If allowed to overflow, it consists of a counter that forces an internal and asynchronous reset to all on-chip peripherals. The counter also optionally asserts the RESET\_B pin to reset external devices and circuits. The watchdog counter must not overflow if the software code works well and services the watchdog to restart the actual counter.

The EWM does not reset the CPU and peripherals of the MCU, making it different from the internal watchdog.

#### 4.2.8 14-bit DAC and 12-bit DAC

LPC556x series do not integrate DAC.

LPC553x has three instances of the 12-bit 1 Msps DAC module, DAC0, DAC1, and DAC2 with a compatible DAC controller.

MCX Nx4x has two instances of the 12-bit 1 Msps DAC module, DAC0, DAC1, with a compatible DAC controller.

MCX Nx4x has of the 12-bit 1 Msps DAC module, with a compatible DAC controller.

MCX Nx4x has one instance of the 14-bit 10 Msps DAC module, DAC2, with a compatible DAC controller.

#### 4.2.9 SINC filter

LPC55xx series do not integrate with SINC Filter, but MCX N series have this feature.

SINC converts an external ADC sigma-delta modulator bitstream to a data stream. The converters are based on:

- A maximum of 3-order sinc digital decimation filters with FastSinc support.

- A maximum selectable Over Sampling Ratio (OSR) of 2048.

You can combine SINC functionality with more software-based filtering.

#### 4.2.10 Touch Sensor Interface (TSI)

LPC55xx series do not integrate with TSI, but MCX N series have this feature.

TSI provides touch sensing detection on capacitive touch sensors. The external capacitive touch sensor is typically formed on a Printed Circuit Board (PCB) and the sensor electrodes are connected to TSI input channels through the I/O pins in the chip. The TSI module operates in a switching-integration style to achieve low-power, high-sensitivity, and advanced ElectroMagnetic Compatibility (EMC) robustness.

The module supports:

Self-Capacitance mode: In this mode, TSI requires only one pin for each touch sensor.

All information provided in this document is subject to legal disclaimers.

#### Migration Guide from LPC55xx to MCX Nx4x

Mutual-Capacitance mode: In this mode, TSI performs sensing using a capacitive touch matrix in various TX-RX configurations. TSI requires one pin per TX and RX line.

TSI fully supports the NXP touch library based on SDK, which provides a solid capacitive measurement module for the implementation of touch keyboard, rotaries, and sliders.

#### 4.2.11 FlexIO

LPC55xx series do not integrate with FlexIO, but MCX N series have this feature.

The FlexIO module was first introduced in the Freescale Kinetis KL43 family. It can emulate various serial communication protocols including: UART, SPI, and I<sup>2</sup>C. The FlexIO module is flexible, and you can configure it according to your communication needs. The main components of the FlexIO module are the shifters, timers, and pins. Data is loaded onto a shifter and a timer is assigned to generate the shifter clock and use a pin to output the data from the shifter.

#### 4.2.12 Ethernet

LPC55xx series do not integrate Ethernet. MCX N series has one instance of the Ethernet QoS module, ENET0.

The Ethernet module enables a host to transmit and receive data over Ethernet in compliance with the IEEE 802.3-2008 standard. The Ethernet interface contains a fully-featured 10 Mbps or 100 Mbps Ethernet Media Access Controller (MAC) designed to provide optimized performance by using the DMA hardware acceleration.

#### 4.2.13 USBDCD

LPC55xx series do not integrate with USBDCD feature, but MCX N series have this feature.

USBDCD works with the USB transceiver to detect whether the USB device is attached to a Charging Port, either a Dedicated Charging Port (DCP) or a Charging Downstream Port (CDP). The system software coordinates the detection activities of the module and controls an off-chip integrated circuit that performs the battery charging.

#### 4.2.14 EMVSIM

LPC55xx series do not integrate EMVSIM. MCX N series have two instances of the EMVSIM module, EMVSIM0, and EMVSIM1.

EMVSIM facilitates communication with smart cards that are compatible with these standards:

- EMV v4.3 (Book 1)

- ISO/IEC 7816-3

#### 4.2.15 SmartDMA

LPC55xx series do not integrate SmartDMA in official document. MCX N series has one SmartDMA.

SmartDMA is a core that supports unique, reduced instruction sets. It works in a similar way to the Arm core. Being the controller of the AHB matrix, SmartDMA can access:

· All its targets.

The GPIO peripheral control and data registers.

The purpose of SmartDMA is to perform event- and I/O-driven handling to offload the Arm processor in the system.

AN14249

Migration Guide from LPC55xx to MCX Nx4x

#### 4.2.16 Coolflux BSP32

LPC55xx series do not integrate Coolflux BSP32. MCX N series has one Coolflux BSP32 co-processor.

The CoolFlux BSP32 is a programmable digital signal processor, where BSP stands for Baseband Signal Processor and the 32 indicates that is has a 32-bit data path and 32-bit data memories. It is a dual Harvard, dual multiplier processor based on the ultra-low power CoolFlux architecture. It supports 16-bit and 32-bit scalar operations as well as complex and SIMD operations and data types. CoolFlux BSP32 is fully programmable in C and comes with an optimizing compiler and tool suite.

#### 5 Boot mode

#### 5.1 Serial downloader mode

Both MCX Nx4x and LPC55xx chips have the serial downloader mode feature. The serial downloader provides a means to download a program image to the chip via a USB or UART serial connection. In this mode, a host PC can communicate with the ROM bootloader using the serial download protocol. You may use the blhost tool to run the serial downloader. The serial downloader tool is useful in mass production.

#### 5.2 Serial downloader mode

Table 6. Comparison of boot device

| _        | Boot device                                                                     | Description                                                                                             |

|----------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| MCX Nx4x | Internal flash<br>Serial Nor flash via FlexSPI<br>Serial Nand flash via FlexSPI |                                                                                                         |

| LPC553x  | Internal flash<br>Serial Nor flash via FlexSPI<br>Serial Nand flash via FlexSPI |                                                                                                         |

| LPC556x  | Internal flash                                                                  | Most LPC55xx chips support booting only from the internal flash. LPC55xx has serial flash recover boot. |

For more information about the MCX Nx4x boot, see the chip reference manual.

# 6 Development environment and tools

#### 6.1 Software-supported packages and tools

Table 7. Comparison of software-support packages and tools

|            | MCX Nx4x                                   | LPC55xx                                    | Description                                                              |

|------------|--------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------|

| SDK        | MCUXpresso SDK                             | MCUXpresso SDK                             | Providing the drivers and examples for the MCX N4x4 and LPC55xx chips.   |

| IDE        | IAR KEIL MCUXpresso GCC visual studio code | IAR KEIL MCUXpresso GCC visual studio code | Providing the development IDEs to program, compile, debug, and download. |

| Debug tool | J-Link                                     | J-Link                                     | Used to debug the software on the chips.                                 |

AN14249

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved

#### Migration Guide from LPC55xx to MCX Nx4x

Table 7. Comparison of software-support packages and tools...continued

|                      | MCX Nx4x    | LPC55xx     | Description                                                                                               |

|----------------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------|

|                      | ULINK2      | ULINK2      |                                                                                                           |

|                      | DAP-Link    | DAP-Link    |                                                                                                           |

|                      | MCU-Link    | MCU-Link    |                                                                                                           |

| Serial download tool | blhost.exe  | blhost.exe  | Like the MFG tool, it is used to program images to the boot devices directly using the serial downloader. |

| Image tool           | elftosb.exe | elftosb.exe | Used to generate bootable images, including signed or encrypted images.                                   |

# 7 Hardware design

# 7.1 Power supply

### 7.1.1 Power supply on MCX Nx4x chips

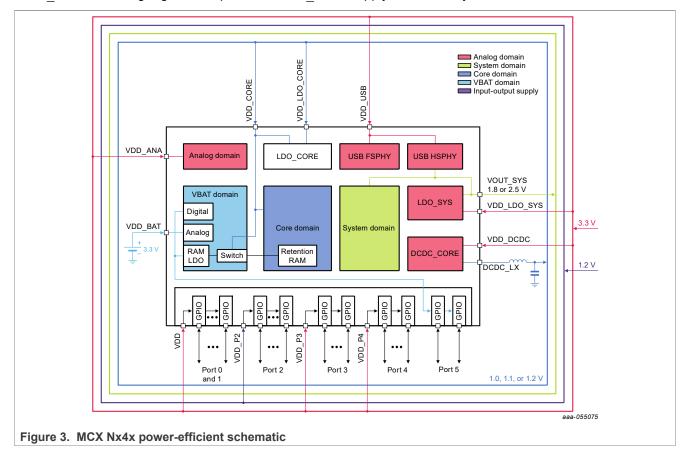

MCX Nx4x supports two kinds of power supply mode, power-efficient supply mode, and low-cost supply configuration.

Figure 3 shows a power-efficient configuration of the chip power supplies. This configuration uses the on-chip DCDC CORE switching regulator to power the VDD CORE supply rail efficiently.

#### Migration Guide from LPC55xx to MCX Nx4x

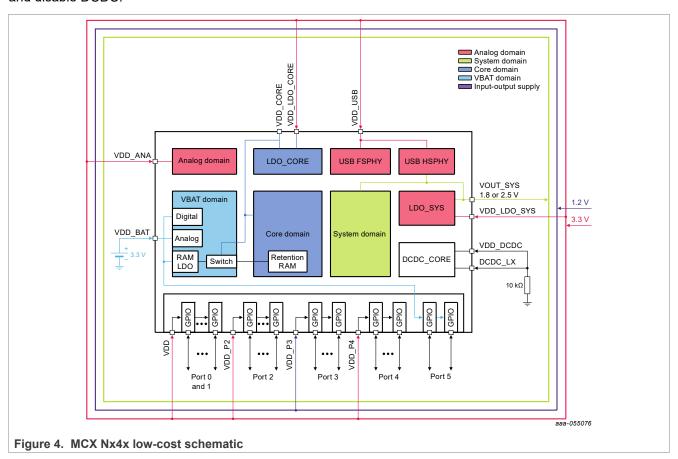

<u>Figure 4</u> shows a low-cost configuration of the chip power supplies. This configuration uses the on-chip LDO\_CORE regulator to save cost and eliminate the passive components for the DCDC\_CORE regulator.

For packages where  $VDD\_DCDC$  has an independent pin, you can connect  $VDD\_DCDC$  and  $DCDC\_LX$  to GND with a  $10-k\Omega$  resistor to disable DCDC. Your software must disable DCDC.

For packages where VDD\_DCDC and VDD\_LDO\_SYS share a package pin, to disable DCDC, float the DCDC\_LX and disable DCDC.

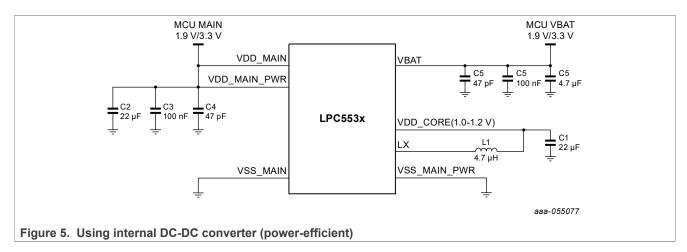

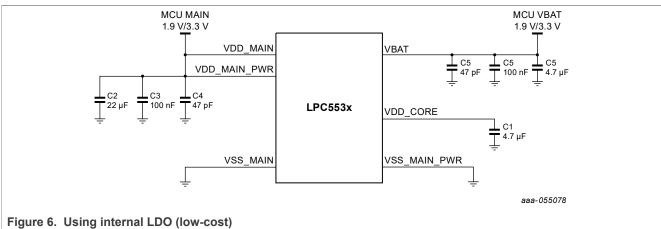

#### 7.1.2 Power supply on LPC55xx chips

All LPC55xx series support the internal DC-DC converter power supply mode, except LPC553x.

LPC553x supports the internal DC-DC converter power supply mode and internal LDO power supply mode.

#### Migration Guide from LPC55xx to MCX Nx4x

#### 7.2 Oscillator design

Table 8. Oscillator design

|                   | MCX Nx4x                                                                                                         | LPC55xx                                                                                             |

|-------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Oscillator design | Supporting the external oscillator range at 16 MHz to 50 MHz                                                     | Supporting the external oscillator range at 16 MHz or 32 MHz.                                       |

|                   |                                                                                                                  | Supporting the software-configurable capacitor bank.                                                |

|                   | Supporting the external 32.768-kHz oscillator (OSC32k) OSC32k supports the software-configurable capacitor bank. | Supporting the external 32.768 kHz oscillator. Supporting the software-configurable capacitor bank. |

**Note:** Only a certain frequency (16 MHz) works with USB ISP on LPC5500 series. The USB ISP must configure the clock frequency in CMPA on MCX Nx4x if the non-default (24 MHz) crystal is used.

#### 7.3 Wakeup timing

Table 9. Comparison of wakeup timing

|         | Sleep  | Deep sleep | Power down | Deep power down |

|---------|--------|------------|------------|-----------------|

| LPC553x | 3.2 µS | 76 μS      | 405 μS     | 2.9 mS          |

AN14249

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

#### Migration Guide from LPC55xx to MCX Nx4x

Table 9. Comparison of wakeup timing...continued

|          | Sleep   | Deep sleep | Power down | Deep power down |

|----------|---------|------------|------------|-----------------|

| LPC556x  | 0.5 μS  | 64 μS      | 346 µS     | 4.6 mS          |

| MCX Nx4x | 0.22 μS | 8.7 μS     | 9.8 μS     | 5.3 mS          |

#### 7.4 Package/Pinout differences

The MCX Nx4x device offered 100HLQFP package and 184VFBGA package.

The LPC553x device offered 48HVQFN package and 100HLQFP package.

The LPC556x device offered 64HTQFP package, 98VFBGA package, and 100HLQFP package.

The drawing for the package can be found in the data sheet.

#### 7.5 Minimum system consideration

There are some additional hardware considerations when migrating from LPC55xx to MCX Nx4x.

The LPC55xx and MCX Nx4x devices have the similar reset, ISP, and debug circuit for the minimum system, but for the power supply circuit, in the DC-DC mode, components are different at values.

#### 8 Conclusion

This document describes the differences between the MCX Nx4x and LPC55xx chips. When migrating from LPC55xx to MCX Nx4x chips, consider the differences described in this document.

#### 9 Reference

- MCXNx4x Hardware Design Guide (document UG10092)

- DCDC Usage on MCXNx4x/Nx3x (document AN14185)

- Hardware Design Guidelines for LPC55(S)xx Microcontrollers (document AN13033)

- Hardware Design Guidelines for LPC553x/LPC55S3x Microcontrollers (document AN13707)

# 10 Revision history

Table 10 summarizes the revisions to this document.

Table 10. Revision history

| Document ID | Release date  | Description            |

|-------------|---------------|------------------------|

| AN14249 v.1 | 02 April 2024 | Initial public release |

#### Migration Guide from LPC55xx to MCX Nx4x

# **Legal information**

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="mailto:PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

AN14249

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

### Migration Guide from LPC55xx to MCX Nx4x

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile — are trademarks and/or registered trademarks of Arm Limited (or its subsidiaries or affiliates) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved.

CoolFlux — is a trademark of NXP B.V.

CoolFlux DSP — is a trademark of NXP B.V.

EdgeLock — is a trademark of NXP B.V.

Freescale — is a trademark of NXP B.V.

IAR — is a trademark of IAR Systems AB.

Kinetis — is a trademark of NXP B.V.

**MCX** — is a trademark of NXP B.V.

$\mbox{\bf Microsoft}, \mbox{\bf Azure,} \mbox{ and } \mbox{\bf ThreadX} \mbox{\bf --} \mbox{ are trademarks of the Microsoft group of companies.}$

# Migration Guide from LPC55xx to MCX Nx4x

# **Contents**

| 1      | Introduction                         | . 2 |

|--------|--------------------------------------|-----|

| 2      | Chip comparison                      | . 2 |

| 2.1    | MCX Nx4x series overview             | . 2 |

| 2.2    | LPC55xx series overview              | . 2 |

| 2.3    | High-level comparison                | . 2 |

| 3      | System modules comparison            |     |

| 3.1    | Memory system difference             |     |

| 3.1.1  | Memory system on LPC55xx             |     |

| 3.1.2  | Memory system on MCX Nx4x            |     |

| 3.1.3  | Memory system comparison             |     |

| 3.2    | Clocking differences                 |     |

| 3.2.1  | Clocking diagram on LPC55xx          |     |

| 3.2.2  | Clocking diagram on MCX Nx4x         |     |

| 3.2.3  | Clock feature comparison             | .7  |

| 4      | Peripheral module comparison         |     |

| 4.1    | Changed modules                      |     |

| 4.1.1  | SYSCON                               |     |

| 4.1.2  | Internal Flash Memory                |     |

| 4.1.3  | IOCON to PORT comparison             |     |

| 4.1.4  | GPIO                                 |     |

| 4.1.5  | Real Time Calendar (RTC)             |     |

| 4.1.6  | Low-power Timer (LPTMR) and WKT      | .9  |

| 4.1.7  | I3C                                  |     |

| 4.1.8  | Controller Area Networ (CAN)         | . 9 |

| 4.1.9  | Flexcomm and LP_Flexcomm             |     |

| 4.1.10 | I2S and Serial Audio Interface (SAI) |     |

| 4.1.11 | DMIC and MICFIL                      | 10  |

| 4.1.12 | USB                                  |     |

| 4.1.13 | Secure Digital Input Outpu (SDIO)    |     |

| 4.1.14 | Semaphores2 (SEMA42) and Inter-CPU   |     |

|        | mailbox                              | 10  |

| 4.1.15 | Direct Memory Access (DMA)           |     |

| 4.2    | New modules                          |     |

| 4.2.1  | Core Mode Controller (CMC)           | 10  |

| 4.2.2  | Interrupt Monitor (INTM)             |     |

| 4.2.3  | Error Injection Module (EIM)         | 11  |

| 4.2.4  | Error Recording Module (ERM)         | 11  |

| 4.2.5  | Event Generator (EVTG) and AOI       |     |

| 4.2.6  | Neural Processing Unit (NPU)         |     |

| 4.2.7  | External Watchdog Monitor (ÉWM)      |     |

| 4.2.8  | 14-bit DAC and 12-bit DAC            | 12  |

| 4.2.9  | SINC filter                          |     |

| 4.2.10 | Touch Sensor Interface (TSI)         | 12  |

| 4.2.11 | FlexIO                               |     |

| 4.2.12 | Ethernet                             |     |

| 4.2.13 | USBDCD                               | 13  |

| 4.2.14 | EMVSIM                               | 13  |

| 4.2.15 | SmartDMA                             | 13  |

| 4.2.16 | Coolflux BSP32                       | 14  |

| 5      | Boot mode                            |     |

| 5.1    | Serial downloader mode               |     |

| 5.2    | Serial downloader mode               | 14  |

| 6      | Development environment and tools    | 14  |

| 6.1   | Software-supported packages and tools | 14 |

|-------|---------------------------------------|----|

| 7     | Hardware design                       | 15 |

| 7.1   | Power supply                          | 15 |

| 7.1.1 | Power supply on MCX Nx4x chips        | 15 |

| 7.1.2 | Power supply on LPC55xx chips         | 16 |

| 7.2   | Oscillator design                     |    |

| 7.3   | Wakeup timing                         | 17 |

| 7.4   | Package/Pinout differences            |    |

| 7.5   | Minimum system consideration          | 18 |

| 8     | Conclusion                            |    |

| 9     | Reference                             | 18 |

| 10    | Revision history                      | 18 |

|       | Legal information                     |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.