# **Technology White Paper**

# System Interconnect Fabrics: Ethernet versus RapidIO® Technology

By Greg Shippen, System Architect

Freescale Semiconductor's Digital Systems Division, NCSG

Member, RapidIO Trade Association

Technical Working Group and Steering Committee

#### **Foreword**

An important trend in the embedded industry is the move from proprietary solutions toward standard interconnects and mechanicals (e.g. ATCA, Ethernet, RapidIO®). Traditionally, Ethernet is the incumbent interconnect technology for embedded systems, yet the existence of alternatives has been driven by the realization that some high-performance applications exceed the limits of this traditional protocol. The RapidIO standard, with growing switch, DSP and processor endpoint support, has been deployed in many applications and continues to gain widespread support. RapidIO is particularly popular in wireless infrastructure equipment, where DSP connectivity is critical. As Ethernet and RapidIO continue to evolve, a comprehensive review and comparison is needed to help designers evaluate and select the protocol that best suits their next-generation designs.

This white paper, *System Interconnect Fabrics: Ethernet Versus RapidIO Technology*, is a comprehensive compilation of embedded interconnect information. It provides a high-level market perspective and delivers a detailed technical examination of these two technologies. The paper begins with a top-level description of market requirements for the logical, transport, and physical layers, then moves into a thorough discussion of each protocol.

The author builds a foundation for comparison and discussion through an historical overview of both RapidIO and Ethernet. Understanding the origin of these two standards helps to clarify their current use in embedded applications. A hierarchical side-by-side comparison of the two technologies provides detailed technical data, starting with the logical layer, then moving to the transport and physical layers. Within each comparison is a discussion of the various distinctions of the interconnects, highlighting significant differences.

In addition to the protocol discussions, this paper examines practical considerations such as power usage, throughput and latency, as well as economic factors related to silicon die size/cost, the volume of silicon shipped, and the size of the silicon and support ecosystems.

The author makes the case for Ethernet to continue gaining strength in the WAN and Internet markets while RapidIO becomes the preferred choice for applications that demand higher levels of performance and quality of service (QoS). In closing, the author provides a list of value propositions that should be analyzed by system designers as they evaluate how each interconnect best meets specific application requirements.

System Interconnect Fabrics: Ethernet versus RapidIO Technology delivers a clear and complete analysis that engineers will find useful well into the future of these two successful technologies.

--Linley Gwennap, principal analyst of The Linley Group

February, 2007

## **Freescale Semiconductor**

# **Application Note**

Document Number: AN3088

Rev. 0, 02/2007

# System Interconnect Fabrics: Ethernet Versus RapidIO® Technology

Greg Shippen

System Architect

Digital Systems Division, NCSG

Freescale Semiconductor, Inc., Technical Working Group and Member of the RapidIO Trade

Association Steering Committee

Market pressures demand that each new generation of networking and communications system deliver both higher performance and new functionality at a lower price. Increasingly, system providers seek to meet these requirements with industry-standard solutions ranging from protocols and interconnects to mechanical designs.

In many networking and wireless applications, Ethernet is the first interconnect technology considered. However, recent alternatives such as RapidIO® have now become viable. RapidIO technology offers several advantages over 1G and 10G Ethernet:

- · Low CPU overhead

- Higher effective bandwidth

- Superior Quality-of-Service

- Superior latency and latency-jitter characteristics

- Competitive or lower cost

- Growing ecosystem

This document reviews the use of Ethernet and RapidIO technology as a system interconnect fabric, comparing them against the requirements for such fabrics. Quantitative analysis is presented where possible. A LAN or WAN setting is not the focus of this document.

#### Contents

| 1 | Interconnects Everywhere         |     |

|---|----------------------------------|-----|

| 2 | System-Level Fabric Requirements | 4   |

| 3 | Ethernet Technical Overview      | .10 |

| 4 | RapidIO Technical Overview       | .19 |

| 5 | Ethernet and RapidIO Comparison  | .33 |

| 6 | Practical Considerations         | .40 |

| 7 | Conclusion                       | .49 |

| 0 | Pavicion History                 | 51  |

# 1 Interconnects Everywhere

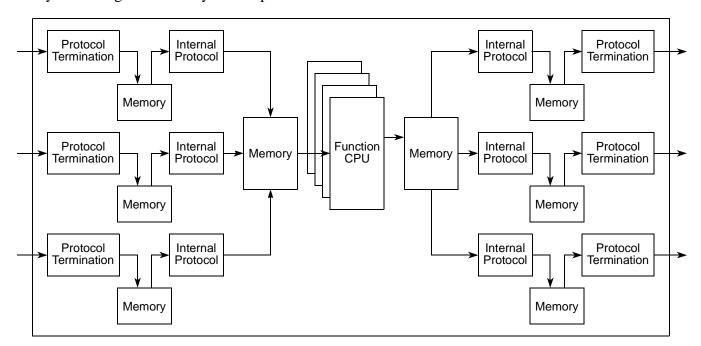

Many networking and communications systems share similar architectural features. Figure 1 illustrates a generic system with a pipeline data flow. External protocols can be terminated at the entry or encapsulated at the boundary of the system and the data temporarily placed into memory arrays. One or more functional units read the data from memory using internal protocols and then transform it in application-specific ways before again placing it into temporary storage. From here the system moves this data to the exit point of the system using an externally visible protocol.

Figure 1. Generic Embedded Communications System

At each step in the pipeline from entry to exit an interconnect protocol is required. As systems grow more complex, the variety of interconnects grows as well, requiring increased engineering costs to design and support them. As Moore's Law increases the speed and complexity of functional blocks, interconnects can become a bottleneck, especially interconnects between ICs and boards. Clearly, increasing interconnect performance is critical to increasing system performance.

While interconnects have a direct impact on achievable system performance, cost often determines the performance and feature set delivered in a product. Reducing the cost of interconnects at a given performance point brings an opportunity either to reduce product cost or invest the savings by increasing performance or adding new features. Industry standards open the door to lower cost in several ways. Standards enable multi-vendor interoperability and thus increase competition. They also allow amortization of engineering costs such as intellectual property (IP) development across a larger ecosystem. When a standardized technology becomes widely used, there is greater potential for lowering costs. An interconnect that can replace IC connections with a system-level backplane logically has the potential to lower costs.

As Figure 1 suggests, a variety of interconnects and protocols often exist in embedded systems. Reducing the number of different interconnect types reduces development and recurring product costs as well. This reduction requires an interconnect flexible enough for wide use in a system.

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

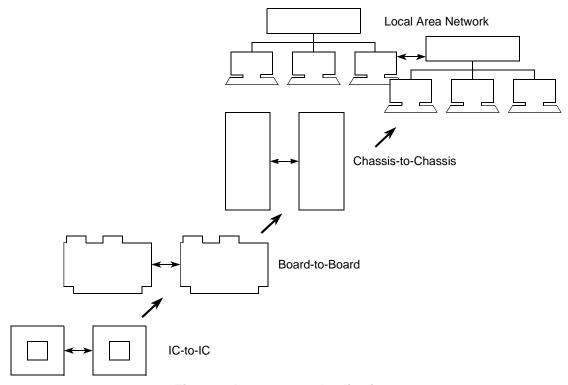

As Figure 2 shows, interconnects can be classified into four applications depending on their position in the architectural hierarchy:

- IC-to-IC

- Board-to-board

- Chassis-to-chassis

- Local area network

Figure 2. Interconnect Applications

Many proprietary interconnects are optimized for just one of these applications. Using them elsewhere can often incur significant performance and product costs. For example, using a processor front-side bus originally intended to interconnect a CPU, main memory, and I/O system as a system-wide interconnect can be challenging at best and impossible at worst.

A number of standard interconnects have been developed. Early arrivals included 10/100 Mbps Ethernet, TDM, and VME. More recently, standards such as CSIX, HyperTransport, Infiniband, PCI Express, RapidIO, and SPI4-2 have garnered industry support. Two considerations for gauging the ability of any interconnect to meet cost and performance goals as a system fabric are silicon-support ecosystem and technical viability. At first, the interconnect with the largest ecosystem may seem most likely to meet these goals. After all, a large ecosystem should ensure that the technology road map is broad and well invested. Using this measure, the best choice often appears to be Ethernet. For many system applications, Ethernet is indeed a suitable choice. However, the limitations of Ethernet make it challenging to meet certain system-level requirements. For some applications, RapidIO technology is a better solution. A variety of technical advantages contribute to the growing support of RapidIO technology in system applications. This document reviews system fabric requirements and then compares how well Ethernet and RapidIO technology can meet these requirements.

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

# 2 System-Level Fabric Requirements

A system interconnect necessarily engages a broader set of requirements than smaller subsystems. Reviewing common system fabric requirements can help us to sort out the suitability of Ethernet or RapidIO as a system fabric.

## 2.1 Data Plane Versus Control Plane

Most networking and communications systems comprise two often separate system architectures and fabrics: the data plane and control plane. The data plane moves traffic through high bandwidth paths from a remote source to a remote destination. Generally, data plane traffic is not consumed by the system. Often, the data plane must carry this traffic with some degree of Quality of Service (QoS). In the most demanding setting, a previously agreed minimum bandwidth must be guaranteed for some or all traffic.

The obvious measure and requirement on a data plane interconnect is sustained bandwidth. Also of importance is the ability to minimize packet loss, latency jitter, and in some cases end-to-end latency. Achieving high bandwidth in a carrier-grade data plane application often implies the ability to control congestion and partition available bandwidth on a fine-grained basis.

The control plane carries traffic that is generated and consumed locally in the system. Often, this traffic is used to initialize the system and manage run-time errors or to supervise system operation. In some applications, it also directs data plane traffic flow or carries unusual data traffic. Control plane traffic is processor-oriented. Dedicated compute resources communicate with each other while performing complicated system-level control and management algorithms. Not surprisingly, many control plane interconnects derive from processor front-side or I/O buses designed to carrying a combination of processor, memory, and I/O traffic.

The most obvious control plane interconnect requirement is low latency. Completing control algorithms promptly requires system reliability, performance, and predictability. Minimizing latency requires low communication overhead and careful protocol design. Because the control plane is processor-centric, usage paradigms such as address-based read/write and messaging are vital to minimize processor overhead.

Another common requirement is guaranteed delivery. Unlike data plane traffic that can tolerate occasional packet loss, control plane traffic must have robust error detection and hardware correction to reduce the impact of soft errors.

Many systems use dedicated fabrics to move control and data plane traffic. Ideally, to simplify the system and reduce costs, traffic for both would traverse the same interconnect. However, such use can affect system reliability because a failure of both control and data paths affects the ability of the system to diagnose and work around the failure. When reliability and cost requires a combined fabric, a combination of protocol features for both control and data plane traffic is a must.

# 2.2 Layered Specification Architecture

Some types of embedded equipment have extended 5–10 year product lifetimes. To allow subsystem upgrades and derivative products, a system interconnect should meet evolving requirements over multiple generations of products.

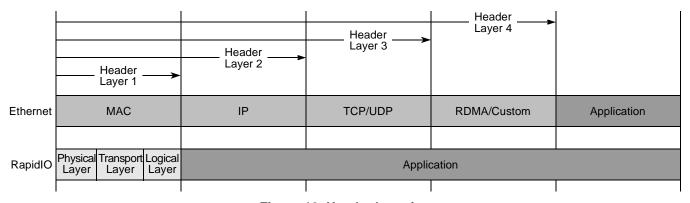

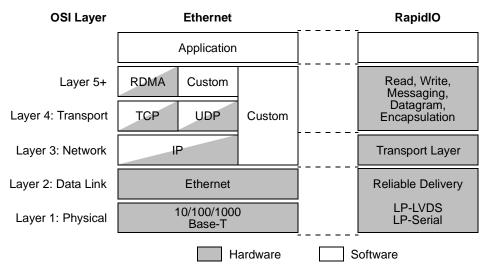

Over time, a hierarchical layered protocol became generally accepted for the sake of long-term flexibility. In this approach, the protocol is partitioned hierarchically as shown in Figure 3. Each layer presents an abstracted set of services upward to higher layers. Therefore, for example, the physical layer can be updated without entailing higher-level hardware and software changes.

The most well-known example of layered hierarchical partitioning is the OSI reference model. Many protocols use variations of this model. In the case of Ethernet and RapidIO technology, each partitions the layers somewhat differently. To discuss them using common terms, this application note defines three general layers that map to one or more layers in the OSI stack as shown in Figure 3.

|         | Layered<br>OSI<br>Architecture | Common<br>Architecture |

|---------|--------------------------------|------------------------|

| Layer 7 | Application                    | Application            |

| Layer 6 | Presentation                   | Аррисацоп              |

| Layer 5 | Session                        | Logical                |

| Layer 4 | Transport                      | Logicai                |

| Layer 3 | Network                        | Transport              |

| Layer 2 | Data Link                      | Physical               |

| Layer 1 | Physical                       | Filysical              |

Figure 3. Architectural Layers

Upper-layer hardware or software applications invoke logical-layer operations. The transport layer then sets header fields necessary to route resulting packets to the intended destination. Finally, the physical layer adds fields required by the link protocol to move the packet reliably from one side of the link to the other.

Protocol extensibility is not only layered and hierarchical; it requires "future proofing" so that new features can be added without breaking backward compatibility. Defining spare bits has long been a common solution. However, more than one protocol has been prevented from using spare bits when a specification does not require all devices to set reserved bits in the header to a known state and then to ignore them when interpreting the header. This simple requirement allows new devices to anticipate the state of reserved bits generated by early silicon and act in a backward-compatible way.

# 2.3 Logical Layer Requirements

The logical layer defines services that move data from one device or endpoint to another. Control and data plane applications use the services appropriate to their tasks. For example, control plane applications often depend on guaranteed delivery.

Data plane applications do not always require guaranteed delivery and may tolerate loss of some packets. Common data plane services include:

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

### System-Level Fabric Requirements

- *Data streaming*. Sometimes called datagram services. Conceptually, datagrams convey an ordered stream of data moving from some source to a destination endpoint FIFO. Similar to messaging, datagrams carry a limited amount of data and do not have an associated address.

- Remote DMA. Moves data between two endpoints using read or write semantics. It is optimized to move large blocks of data by moving data directly from the source to the destination without the need to copy data from an inbound buffer to the final location in memory

- *Protocol and payload encapsulation*. Allows external protocols and payloads to be carried across an interconnect, often transparently so that the external protocol is unaware of the existence of the intervening interconnect.

- *Traffic management*. Allows entry and exit points in the network to communicate in order to allow negotiation of fabric services such as bandwidth and QoS.

## Common control plane services include:

- *Read and write*. Allows an exchange of data between endpoints. The address of the data to exchange is carried from source to destination.

- *Messaging*. Similar to a write, allows a data payload to be sent from source to destination. Unlike writes, messages do not have an associated address but rely on the destination endpoint to define where in memory to place the associated data.

- Atomics and other distributed computing functions. Support semaphore services that coordinate distributed processing. Additional services keep caches and other processor-related state coherent across a fabric.

- *Multicasting*. Can be very useful for system management functions or distributed computing settings. The duplication of data can occur in endpoints or switches

# 2.3.1 Transaction Ordering Policy

System-wide ordering policy is determined by application-level requirements and affects both performance and compatibility with existing software. Strict ordering is compatible with most software mechanisms. However, as ordering rules become weaker, more opportunities exist to reorder traffic and increase performance.

Most software executes sequentially line-by-line in a single control thread in which the effects of one line are assumed to be complete before the next line of code executes. A read operation on one line is expected to reflect updates from writes in previous lines of code. From a system fabric perspective, a read request transaction cannot pass earlier writes but instead must push them ahead.

Other software paradigms involving multiple entities, such as the producer-consumer mode, assume certain system-level ordering conventions. To coordinate the movement of data between two masters, the producer-consumer algorithm expects the producer to update a buffer before it notifies the consumer. Remember, from a system fabric perspective, a read response (producer notification) cannot pass producer writes (buffer data) but instead must push write transactions ahead.

When specific ordering rules are imposed on a system and fabric, how and where they are enforced is an important consideration when dealing with protocol complexity and performance.

# 2.4 Transport Layer Requirements

The transport layer defines how destination endpoints are addressed and packets are routed from source to destination across the fabric. Requirements for a system fabric using a point-to-point interconnect include:

- Addresses a large number of nodes

- Destination-based routing

- Simplified switches

The transport layer for a chassis-sized system fabric must support up to thousands of nodes. Given the trade-off between header overhead and addressable space, support for more nodes is not a requirement.

Two common routing mechanisms are destination routing and path-based routing. Destination routing implies lookup tables at switching elements. Path-based routing carries the desired path for the packet in the header. As a result, all endpoints must know the system topology. Therefore, path-based routing cannot contain runtime topology changes to limited regions of the network. For example, a hot-insertion or extraction in a destination routed system would require changes to state in adjacent switches rather than every endpoint in the system.

To connect more than two devices, shared bus interconnects require little more than additional copper on the board. Duplicating this connectivity in a point-to-point interconnect requires a low-cost switch device. Reducing switch complexity and therefore cost is a priority.

The interconnect protocol can have a strong impact on switch complexity. For example, complexity increases with a need for complex header parsing or the need to modify each packet as it passes through a switch.

Some types of traffic can tolerate occasional packet loss. For example, real-time data such as voice and video can suffer some data loss without becoming bothersome at the application level. Other types of traffic have great difficulty tolerating loss. For example, loss of a control plane message often means long upper-layer timeouts that can introduce unacceptable control-loop latencies. Unlike predictable and structured user data streams, it can be difficult to determine how to recover promptly after an error when the control algorithm is distributed across multiple processors. A system interconnect that carries both data and control plane traffic must accommodate both lossy and lossless transport. Ideally, correcting for packet loss can be done in hardware rather than in software stacks, which may inject considerable latency when correcting errors.

# 2.5 Physical Layer Requirements

The physical layer of an interconnect defines how data payloads are transported from one side of a link to another. This definition includes the link protocol as well as the signaling used on the electrical channel.

The length of the physical channel has a strong influence on complexity and cost. Sending a gigabit per second bit stream over hundreds of meters of unshielded cable requires a very different solution than sending that same bit stream across a one meter backplane. For most networking and communications equipment, the physical channel length ranges from tens of centimeters between chips to between 80 and 100 centimeters across a standard rack-mounted backplane. To minimize costs, it is desirable to achieve these distances using standard FR-4 circuit board material. For some applications, the need to span chassis assemblies within a rack makes a cable channel of up to 10 meters desirable.

System Interconnect Fabrics: Ethernet Versus RapidIO<sup>®</sup> Technology, Rev. 0

### System-Level Fabric Requirements

To minimize the number of signals, there is a serialized embedded clock signaling scheme that uses a single differential pair in each direction. To scale bandwidth without increasing the data rate per pair, multiple single pairs or "lanes" can be used together as a single logical link. The routability of a cost-sensitive backplane imposes a practical limit of about four lanes between cards. Therefore, single and four lane support is a requirement. However, some board-level chip-to-chip applications can use sixteen lanes or more per link for maximum bandwidth. Support for two, eight, and sixteen lanes offers added flexibility. The ability to operate when only some of the lanes are connected is also highly desirable.

A range of supported lane data rates allows the required throughput to be closely matched to minimize power and cost. In practice, the ability to make a relatively small down shift in data rate late in development can sometimes allow a system to ship even though the physical channel does not have the anticipated design margin.

As increasing data rates stretch the limits of electrical signaling technology, maintaining current bit error rates becomes increasingly difficult. Hardware support for link-level error correction becomes a requirement when guaranteed delivery service with QoS is needed.

Some physical installations must connect equipment across distances longer than copper-based interconnects can accommodate at a given data rate. Because optical fiber is a common physical medium for traversing hundreds or even thousands of meters or more, the ability of an interconnect to accommodate fiber-based physical layers is desirable.

# 2.6 Quality of Service

Quality-of-Service (QoS) requirements are becoming increasingly important in networking and computing equipment. As multimedia services proliferate, new service quality requirements are imposed on system fabrics. For example, real-time video and audio data streams require a minimum guaranteed bandwidth with low end-to-end latency and latency jitter. Real-time interactive streams may also have specific worst-case end-to-end latency requirements. In general, QoS can be measured in terms of throughput, end-to-end latency, and latency jitter. To meet specific requirements based on these metrics, a fabric protocol must be able to:

- Identify individual traffic streams between two endpoints.

- Provide differentiated levels of service to individual streams.

- Control congestion caused by streams as they cross the fabric.

The ability to identify and differentiate traffic in a network is basic to QoS. It is always possible to identify traffic streams based on source and destination endpoint identifiers to allow differentiated service between multiple endpoint pairs. However, most system fabrics must accommodate endpoints that aggregate multiple flows of traffic and therefore need to identify specific flows between any endpoint pair.

After classification of individual streams is accomplished, fabric components must be able to deliver varying levels of service quality based on packet classification.

Delivering minimum guaranteed bandwidth means switches must be able to reserve bandwidth over links for specific classes or streams. This implies that the fabric must have effective flow control mechanisms to combat congestion. The existence of a bandwidth guarantee for one stream implies that other streams have the potential to back up. Congestion control then becomes crucial to delivering guaranteed bandwidth. Controlling latency also requires close control over congestion events because they cause

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

packets both individually and collectively to experience increased latency as they pass through the network.

Ideally, congestion could be eliminated by injecting much less data than the fabric can carry. For this reason, some systems rely on over-provisioning the system fabric to meet required QoS. Unfortunately, congestion can still develop in over-provisioned fabrics when multiple traffic flows converge on a single link or if head-of-line blocking occurs in a fabric implementation.

As link speeds increase, the reliability of individual links is not expected to increase. Theoretical bit error rates of  $10^{-12}$  to  $10^{-15}$  are common today with system-level error rates measured in seconds to hours depending on the number of links in the system. How quickly the fabric detects and recovers from errors can contribute to latency jitter and affect QoS.

Effective system fabrics need robust flow control to minimize latency and achieve high fabric usage. Because congestion is a dynamic phenomenon lasting from nanoseconds to milliseconds, a well-behaved system interconnect must have a hierarchy of flow control methods. The flow control loop latency between the detection of congestion and the traffic source must be short enough relative to the event itself to allow adequate control. Short-term congestion requires very tight flow control loops. The longer the duration of the congestion event, the broader in scope the flow control mechanism must be.

Avoiding short and mid-term congestion events requires moderately broad flow control methods ranging from link level to end-to-end across the fabric. Prevention of longer-term congestion requires that ingress and egress negotiate input and output bandwidth to avoid swamping the fabric. As congestion and head-of-line blocking occur, individual link usage is negatively affected. Unless limited by flow control mechanisms, system throughput can collapse as congestion works its way backward and encompasses large portions of the system fabric.

The highest end-to-end latencies occur when links saturate, leading to full hardware queues. The most effective flow control mechanisms anticipate congestion by watching queue depth and link usage and then proactively controlling traffic flow at entry points. The least effective mechanisms are invoked only after congestion negatively affects network performance.

# 2.7 High Availability

In many embedded applications, the ability to continue operation even in the presence of failures (also known as high availability) is a key customer requirement. Following are the fundamental attributes of any highly available system fabric:

- No single-point failure mechanism with multiple management hosts and redundant endpoints and links

- Robust fault detection at the link level and end-to-end

- Fault recovery with error logging and notification; robust fault isolation and containment

- Hot swap of field replaceable units (FRU)

Highly available system fabrics have no single point of failure and must therefore include redundancy, with management and transport mechanisms. It must be possible to create redundant endpoints and links in either hot or cold standby modes of operation.

System Interconnect Fabrics: Ethernet Versus RapidIO<sup>®</sup> Technology, Rev. 0

#### **Ethernet Technical Overview**

Highly available fabrics must detect and recover from faults ranging from soft errors that occur during normal operation to more catastrophic and rare hard failures. Because soft errors should be the most common error event, highly available fabrics must be able to correct and recover from soft errors.

All layers of the protocol must contribute to fault detection. Link-level error checking and correction should exist. Errors in data payloads and control protocol must be detectable. To recover from lost response transactions, end-to-end transaction timeouts must exist at the logical layer.

To aid in fault recovery, there must be a method to identify failures, log them, and notify a management entity (often a host endpoint somewhere in the fabric). Minimally disruptive debug capabilities should also exist to aid in error diagnosis and recovery. Recovery from hard failures in a system is complicated because simultaneous activities are often affected and must be notified to take recovery action. Minimizing the number of activities affected is crucial to prompt recovery. System fabrics should be able to isolate faults and prevent errant hardware and software from "babbling" into the system by sending transactions indiscriminately through the network and disrupting functional system activities.

When a hard component failure occurs, the fabric must allow hot extraction of the FRU containing the failed component and hot insertion of a new one. Hot swapping at the system level requires the following capabilities:

- Detection and notification of the host manager when a link failure occurs

- Containment of the error from the rest of the system

- Prevention of a failed component from babbling into the system fabric

- Prevention of fabric congestion when data cannot be delivered to the failed component

- Removal of pending transactions to the failed links or component

- Hot removal and reinsertion of an endpoint or switch

- Reinitialization of the link between the system and the newly inserted device

- Reconfiguration of the newly inserted device

Support for hot swapping assumes the existence of system managers that can notify devices communicating with or through a faulty device to stop communication and clean up pending transactions. Managers can use either in or out-of-band mechanisms to carry these commands. Ideally, a system fabric allows in-band fault management even in the presence of system faults because it can reduce system maintenance cost. In all cases, a system manager is involved to coordinate recovery and must itself be redundant in the most aggressive high-availability systems.

# 3 Ethernet Technical Overview

It is doubtful that the originators of Ethernet could have envisaged how widespread their technology would become. As services layered on top of Ethernet become the common language for the Internet, Ethernet is now ubiquitous as both a wide and local area computer interconnect. Also, it has evolved into multiple technical meanings. Ethernet was originally developed by Xerox. Later, Digital Equipment Corporation, Intel, and Xerox released the "DIX" or Ethernet I standard followed later by Ethernet II. Independently, the IEEE® organization created the 802.3<sup>TM</sup> specification that also came to be called Ethernet. The IEEE slightly modified the DIX header format in the 802.3 standard to allow coexistence of both standards in a network.

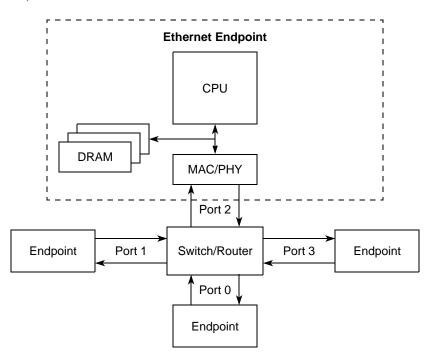

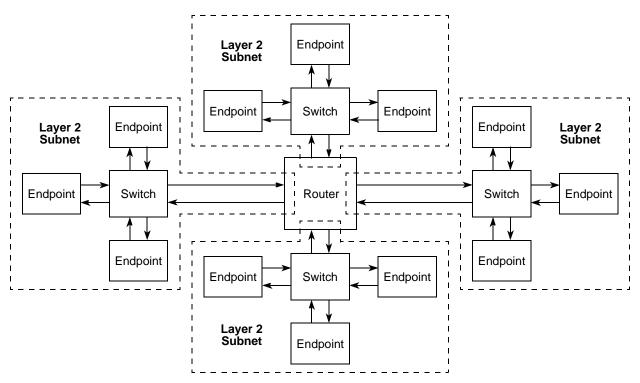

The original deployment model connected a set of closely located computers by a single shared coaxial cable. Taps were attached to the coaxial cable to form drops to each networked computer. As the physical interface (PHY) technology evolved, the physical layer became a point-to-point connection that could be up to 100 meters long. As a result, the deployment model transitioned to point-to-point connections between desktop computers and nearby closets of Ethernet switches or routers configured in a star configuration as shown in Figure 4.

Since its introduction in 1976, the Ethernet PHY layer has been enhanced to support higher and higher data transfer rates. Today, the industry is in a general transition from 10/100 Mbps to 1000 Mbps (1 Gbps) and even 10 Gbps systems beginning to appear in the market. Data is exchanged through packets produced and consumed by endpoints (called "stations" by the IEEE specification). Individual data packets consist of a header and a user payload of between 46 and 1500 bytes. Today, both Ethernet II and IEEE 802.3 header formats are used. The Ethernet II header is the most efficient for carrying commonly used upper-layer protocols such as TCP/IP. As a result, most embedded applications use the Ethernet II format. In the discussion that follows, the Ethernet II format is assumed.

**Figure 4. Ethernet Network**

# 3.1 Original Ethernet Design Goals

The key to Ethernet longevity lies in the set of initial design goals that, in retrospect, seem calculated to guarantee a long-term future:

- Ability to connect many computers

- Simple and inexpensive hardware and software at the endpoints

- Flexible and extensible architecture

Because Ethernet was originally intended to connect computer workstations, the assumption was that a processor at each endpoint could participate in running the protocol. This bias was reinforced by the

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

#### **Ethernet Technical Overview**

limited hardware capabilities of the 1970s, which motivated the trade-off between hardware and software strongly in favor of software. With a limited link-level protocol, the required hardware was relatively simple. This arrangement left a relatively large software stack, especially for upper-layer services. This trade-off imposes a growing performance bottleneck as PHY technology increases in performance.

Perhaps the single most important factor in its longevity is the layered hierarchical architecture of Ethernet, which allows new PHY technology to be introduced without substantial changes to the services on top. Backward compatibility of basic protocol formats was a constant requirement throughout the various PHY generations from the initial common coax cable running at 10 Mbps to today's 1 Gbps and 10 Gbps data rates.

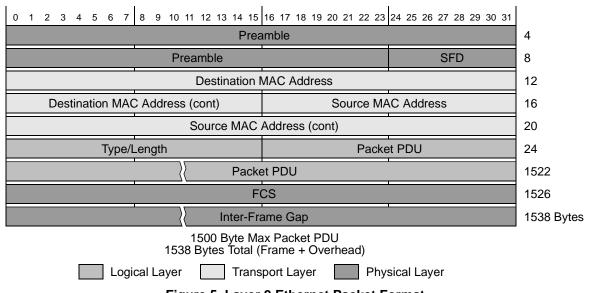

## 3.2 Ethernet Protocol Overview

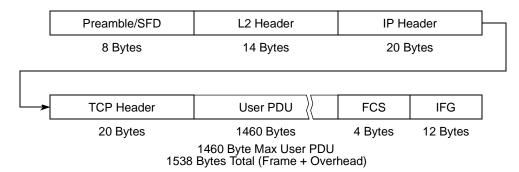

Application data is encapsulated in packets passed between endpoints. Packets are transmitted with intervening InterFrame Gaps (IFG). A packet consists of a preamble and a frame composed of a string of bit fields starting with the destination MAC address and ending with the frame check sequence (FCS). The entire format is shown in Figure 5.

Figure 5. Layer 2 Ethernet Packet Format

The preamble and IFG fields are remnants of the original half-duplex shared coax PHY. The 8-byte preamble carries a specific bit pattern originally used to allow receivers to synchronize their clock recovery circuits. The IFG accommodated the turn-around time necessary for a coax transceiver to shift from transmit to receive and to complete necessary book keeping. The size of this gap is 96 bits or 12 bytes. While more recently-defined PHYs have less need for these fields, they remain for backward compatibility.

The frame header shown in Figure 5 begins with a 48-bit destination and source MAC address. These fields are used to direct packets to their destination and to direct responses back to the source. After the address fields is a Type/Length field. The definition of this field depends on whether the packet uses the IEEE 802.3 or Ethernet II format. The IEEE 802.3 field defines the length of the packet between 64 and 1500 bytes. The Ethernet II field defines the type of payload such as Internet protocol (IP) and use field

System Interconnect Fabrics: Ethernet Versus RapidlO $^{\scriptsize (\!0\!)}$  Technology, Rev. 0

values larger than 1535. The two definitions do not overlap and can coexist in a network. The payload is between 46 and 1500 bytes long. A packet has a minimum size of 64 bytes and must be padded when the actual payload is less than 46 bytes. For error protection, a frame check sequence is appended to the user data. This cyclic redundancy checksum (CRC) value is calculated over the frame, starting with the destination MAC address. There is no required order of delivery or completion in Ethernet. Packets can arrive at the destination out-of-order with respect to the transmission order at the source. If ordering is required, layer 3+ must provide this service.

## 3.2.1 Logical Layer

The Ethernet specification defines up to layer 2 in the OSI stack. The only Ethernet semantic is the unreliable datagram by which user-defined data payloads are streamed across the interface. Packets can be dropped in transit for a variety of reasons. Payloads have no associated memory address.

Because Ethernet implements much of its protocol in software, data movement is orchestrated by a processor that interacts directly with the Ethernet interface hardware. Typically, the processor manages a descriptor-based DMA engine that moves packets in and out of memory. The processor queues up packets or frames that the DMA engine later transfers through the Ethernet interface to a destination.

Applications that need more sophisticated services must layer protocols on top of layer 2. For example, a protocol that performs commanded reads must be implemented before data can be read from a remote endpoint. Many protocols have been created on top of the base layer 2 Ethernet MAC. Some application-level protocols of interest here are listed in Table 1.

| Protocol              | OSI Layer | Service                                     | Added Services                                        |

|-----------------------|-----------|---------------------------------------------|-------------------------------------------------------|

| Sockets               | 5+        | Connection-oriented Reliable                | Software access to TCP/IP services                    |

| RDMA<br>(iWarp, iSER) | 5+        | Connection-oriented Reliable                | Minimized interrupt and copy overhead at the receiver |

| TCP                   | 4         | Connection-oriented Reliable                | Reliable transport Application ports Ordering         |

| UDP                   | 4         | Connectionless<br>Unreliable<br>Best Effort | Payload check summing<br>Application ports            |

| IP                    | 3         | Connectionless<br>Unreliable<br>Best Effort | SAR<br>Type of service                                |

| ARP                   | 2         | Routing support for IP                      | Associates IP with MAC address                        |

| MAC                   | 2         | Connectionless<br>Unreliable<br>Best Effort | Base specification                                    |

**Table 1. Ethernet Protocols**

The IP allows inter-networking across heterogeneous network protocols by defining a new universal endpoint addressing scheme. In addition, IP defines segmentation and reassembly (SAR) support for user payloads up to 64 Kbytes. Use of IP with user datagram protocol (UDP) or transmission control protocol

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

#### **Ethernet Technical Overview**

(TCP) has become nearly synonymous with Ethernet. Many embedded Ethernet applications use TCP because software support is widely available and understood.

TCP over IP (TCP/IP) presents an end-to-end connection-oriented reliable service to an application. In delivering reliable service, it must compensate for frame loss, packet duplication, high latency, out-of-order delivery, and loss of connectivity. As illustrated in Figure 6, TCP/IP adds significantly to the overall Ethernet header. UDP can be used when this overhead is too high and reliable delivery is either unnecessary or implemented in a proprietary way. UDP is often used when applications need access to services not accessible through TCP/IP, such as multicast.

Remote DMA (RDMA) is a relatively new protocol to lower the overhead required at the receiver. RDMA enables memory-mapped transactions that can place data directly into the destination buffer and thus minimize unnecessary copies and associated interrupts. This service is becoming increasingly important for applications that stream data across the Ethernet and directly into application buffers. Applications include compute clustering and storage. Many network-independent applications use standard library calls such as sockets to abstract away much of the underlying network complexity.

Figure 6. TCP/IP Header Format

# 3.2.2 Transport Layer

The transport layer defines how packets move from source to destination endpoint in a network. Ethernet uses destination-based routing. At layer 2, addressing is based on MAC addresses. When IP at layer 3 is used, IP addresses also contribute. Layer 2 networks typically consist of endpoints connected by layer 2 switches. Each endpoint is preassigned a unique MAC address. Packets carry a destination MAC address set by the originating endpoint based on its knowledge of the network. Switches use this field to route packets to the proper destination port using internal routing tables. Because switches do not produce or consume packets, switches are transparent to the network.

Layer 3 IP networks introduce a switching device called a router as shown in Figure 7. Routers are similar to switches but they route packets according to the packet layer 3 IP address. Unlike switches, routers are not transparent to the network. Each port of a router appears to the connected layer 2 network as an endpoint and therefore has a unique associated MAC address.

IP networks replace one or more switches with routers that segment the network into multiple layer 2 sub-networks connected by routers. All packets that traverse a router must carry an IP header that includes a source and destination IP address. Every endpoint keeps a table that associates network IP addresses with a MAC address. The IP address of destinations within the endpoint layer 2 sub-network are associated with

System Interconnect Fabrics: Ethernet Versus RapidlO $^{\circledR}$  Technology, Rev. 0

their assigned MAC address. All other endpoints, which by definition are outside the local sub-network, are assigned the MAC address of the router port connecting the sub-network to the rest of the network.

In a layer 2 network, the MAC address is end-to-end and remains unchanged as a packet traverses the network. In a layer 3 network, the source and destination IP address fields of a packet are end-to-end and remain unchanged as it traverses the network. The MAC addresses of each packet are modified by routers as it traverses the network. Routers contain lookup tables that associate the destination IP address with an output port and a MAC address of an endpoint within the subnetwork connected to that port. Before the packet leaves the router, the router replaces the source MAC address with that of the output port and the destination MAC address with the value associated with the destination IP address of the packet. When the destination is not located within the immediate layer 2 subnetwork, this MAC address is set to another router leading to the final destination.

Many backplane-oriented embedded systems use Ethernet as a fabric to implement layer 2 switch fabrics. However, these fabrics commonly carry packets with IP or some other optimized proprietary layer 3+ protocol. These protocols are often introduced when the fabric must carry layer 3+ traffic to and from external networks.

Figure 7. IP Network

The original Ethernet physical layer was a shared cable using the carrier sense multiple access with collision detection (CSMA/CD) protocol to arbitrate use of the cable. Collisions were an expected part of the arbitration process and they corrupted packet data. The packet was retried up to 16 times. However, packets were still allowed to be dropped to simplify the Ethernet protocol and transfer the recovery burden to higher layers. Today, full duplex point-to-point topologies defined in the 802.3x specification have eliminated collisions. However, packets are still dropped because of soft errors or short term congestion

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

#### **Ethernet Technical Overview**

events that exceed available buffering. No link layer protocol exists to recover a dropped packet. End-to-end protocols such as TCP must provide a reliable delivery service to application layers.

## 3.2.3 Physical Layer

The physical layer consists of the link protocol and the electrical interface between devices. The link protocol moves packets from one side of the link to the other. An Ethernet link itself has a very light protocol. Packets are streamed from transmitter to receiver. The transmitter is free to send packets as fast as possible. With the introduction of the PAUSE frame in the IEEE 802.3x specifications came a flow control method to allow a receiver to slow down the rate of packet transmission (see Section 3.4, "Flow Control").

At the receiver, the preamble field is used to find the beginning of a frame. The receiver checks the frame using the frame check sequence (FCS), an additional checksum used to verify frame integrity, and then examines the header and data payload as needed for further processing. No acknowledgement exists at this level of the protocol and there is no mechanism for communicating link errors back to the transmitter.

The original Ethernet PHY was a half-duplex protocol over a shared coaxial PHY. Additional PHYs have since been specified, as shown in Table 2. Today, most PHYs define a full-duplex point-to-point topology supported over up to 100 meters of twisted pair cable.

|             | Aggregate Data<br>Rate | Encoding                           | Symbol<br>Rate | Number of<br>Differential<br>Channels | Channel                                       |

|-------------|------------------------|------------------------------------|----------------|---------------------------------------|-----------------------------------------------|

| 10Base5     | 10 Mbit/s              | Manchester                         | 10 Mbaud       | 1                                     | Shared Coax                                   |

| 10Base-T    | 10 Mbit/s              | Manchester                         | 10 Mbaud       | 2                                     | 100m Cat3 Cable                               |

| 100Base-Tx  | 100 Mbit/s             | 4B5B + 3-level MLT                 | 125 Mbaud      | 2                                     | 100m Cat5 Cable                               |

| 1000Base-T  | 1000 Mbit/s            | 4D-PAM5                            | 125 Mbaud      | 4                                     | 100m Cat5e Cable                              |

| GigE SERDES | 1000 Mbit/s            | 8B10B +<br>1000Base-CX electricals | 1.25 Gbaud     | 2                                     | Connection to Fiber PHY Backplane FR-4        |

| SGMII       | 1000 Mbit/s            | 8B10B +<br>LVDS electricals        | 1.25 Gbaud     | 2                                     | Connection between endpoint and PHY or switch |

**Table 2. Ethernet PHYs**

10Base5 is the original 10 Mbps Ethernet I PHY. Fast Ethernet (100 Mbps) introduced three PHYs. The media-independent interface (MII) allows the designer to choose which PHY to use with a given controller. This 4-bit wide parallel interface supports 10 and 100 Mbps speeds. Later, this interface was extended to 8 bits to accommodate Gigabit Ethernet data rates.

Today 10Base-T, 100Base-Tx, and 1000Base-T are the most common PHYs. When separate PHY devices exist, MII or GMII are used to connect them to the Ethernet controller. Because MII and GMII require a relatively large number of pins, various standards have arisen to reduce the pin-count. These reduced interfaces include RMII and RGMII. Another very low pin-count standard now widely used for Gigabit Ethernet is the SERDES-based SGMII. Some Gigabit Ethernet switch vendors support SERDES-based interfaces using either SGMII or IEEE 802.3 1000Base-CX short-haul copper electricals. The main

System Interconnect Fabrics: Ethernet Versus RapidlO $^{\scriptsize (\!0\!)}$  Technology, Rev. 0

rationale for these interfaces is to lower pin counts on high-density switch and PHY devices. However, some have leveraged them directly for use in backplane applications.

# 3.3 Quality of Service

As media services on the Ethernet become more sophisticated, the need for effective Quality of Service (QoS) evolves. Among the standard QoS methods for classifying traffic on a per packet basis are:

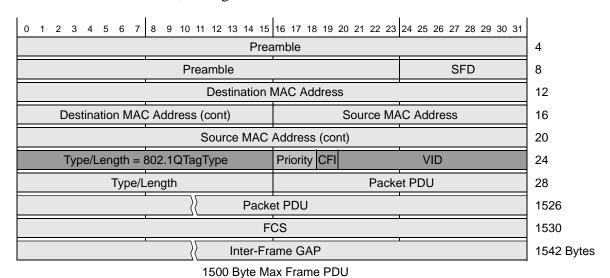

- 802.1p+q VLAN tagging. A layer 2 classification method that adds a 4-byte tag to every frame. As shown in Figure 8, this tag defines a 3-bit priority field for up to eight defined classes of service and a 12-bit VID field to differentiate up to 4096 different streams. Embedded systems frequently use VLAN tagging to differentiate traffic because it is increasingly supported by single-chip layer 2+ switches.

- *Diff-Serv*. A layer 3 classification method that overloads the Type of Service (ToS) field in the IP header and defines up to 64 classes of service.

- *MPLS*. A layer 3 method that involves tagging IP frames at the edge of an MPLS network with a 32-bit value. This tag simplifies routing by representing a specific route through the network. Routers do lookups based on the tag and do not have to parse the header extensively. As the frame leaves an MPLS network, the tag is removed.

1542 Bytes Total (Frame + Overhead)

Figure 8. Layer 2 VLAN Tag

## 3.4 Flow Control

Ethernet is designed for "best effort" service in which packets may be dropped to control congestion or dropped because of errors. As a result, flow control is desirable to control congestion-related packet loss. Initially, flow control in Ethernet existed only as part of layer 3+ services such as TCP. TCP depends on positive acknowledgement messages from the receiver to deliver reliable service. When acknowledgement messages indicate packet loss, it reduces its transmit rate. More recently, Layer 2 MAC control frames were defined in 802.3x to allow the link layers of two connected endpoints to communicate with each other. MAC control frames are normal minimum size 64-byte frames with a unique Type/Length field. The first control frame defines the PAUSE frame that allows an endpoint operating in full-duplex mode to ask

System Interconnect Fabrics: Ethernet Versus RapidIO<sup>®</sup> Technology, Rev. 0

#### **Ethernet Technical Overview**

that the opposite endpoint temporarily stop transmitting frames. Any endpoint receiving a PAUSE frame stops sending all frames except a MAC control for up to 64K minimum frame size periods before resuming normal operation. The specification does not require support for PAUSE frames. An endpoint may support reception of PAUSE frames but not be capable of sending them. The Auto Negotiate protocol discussed later allows endpoints to discover whether the opposite endpoint supports PAUSE.

The IEEE 802.1Qau Task Force is defining additional flow control capabilities within a VLAN. This effort targets embedded and backplane applications. It defines a small Ethernet frame that functions as a backward congestion notification (BCN) message for congestion management.

# 3.5 High Availability

The Ethernet protocol has no inherent single-point failure mechanisms—particularly from the point-of-view of an embedded system. In the wider WAN setting, challenges to high availability include reliability of network management resources. These limited resources must provide naming services and guide routing in a highly dynamic network topology with few network-wide entities overseeing the WAN. Fortunately, embedded systems using Ethernet present a much smaller and more manageable topology and environment.

Ethernet supports redundant paths between any two endpoints either in a hot or cold standby mode. Redundant paths are often used in WAN and LAN networks to increase bandwidth and enhance fault tolerance, so many switches and routers support this capability.

The Ethernet protocol defines the frame check sequence (FCS) at the end of a frame to provide error detection over the entire packet, not including the preamble and IFG. The FCS is checked at each port along the way. If layer 2 switches insert or remove VLAN tags, they must recalculate the FCS in the process. Errors generally cause the packet to be dropped and the error logged using standardized registers. There is no hardware error correction facility. When required, error recovery relies on upper layer end-to-end protocols.

When a fault occurs, in-band notification of management devices is possible if there is sufficient redundancy in the fabric. Some embedded systems use out-of-band mechanisms due to the lossy nature of the transport. For example, the PICMG AdvancedTCA standard defines a management and control interconnect on the backplane in addition to the data plane fabric.

Because MAC addresses are unique to an endpoint, layer 2 Ethernet fabrics require all endpoints in a system to be notified of a change in topology. TCP/IP networks retain a layer of abstraction allowing IP addresses to be retained at endpoints even when the underlying MAC address changes are updated at the routers. Protection from unauthorized and possibly disruptive transactions generated by faulty endpoints is achieved through several mechanisms. Ethernet avoids memory corruption because it has no memory-mapped read and write transactions, and endpoints directly control where inbound datagrams are placed in memory. Because all incoming frames are queued at the receiver, the hardware and network stack must examine each frame and can therefore choose to drop those identified as questionable. In addition, at the transport level VLANs provide some protection by limiting addressability only to a subset of endpoints in the network.

Congestion caused when faulty endpoints inject large amounts of traffic into the network is handled by dropping packets at all points in an Ethernet network. PAUSE frames at the link level and higher level flow control at L3 and above can also be invoked to control this congestion.

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

Hot extraction and insertion is supported by all Ethernet PHYs using the xBase-T PHYs. The Auto Negotiate protocol first defined with 100Base-T in 802.3u allows identification of endpoints and their capabilities as they enter a network. Some mechanical system standards that support Ethernet fabrics provide an out-of-band management interconnect to inform all endpoints communicating with a faulty device to cease communication and clean up pending transactions.

# 4 RapidIO Technical Overview

Motorola started work in 1997 on a next-generation front-side bus for its Power- and PowerPC<sup>TM</sup>-based processors. By 1999, Motorola and Mercury Computer had collaborated to complete the initial RapidIO specification. In 2000, these two companies drove the formation of the RapidIO Trade Association, making RapidIO an independent standard. By 2004, the RapidIO Specification had become an international standard as ISO/IEC 18372:2004.

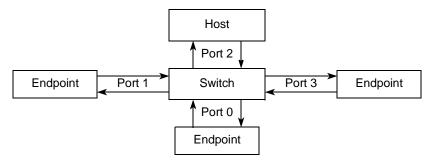

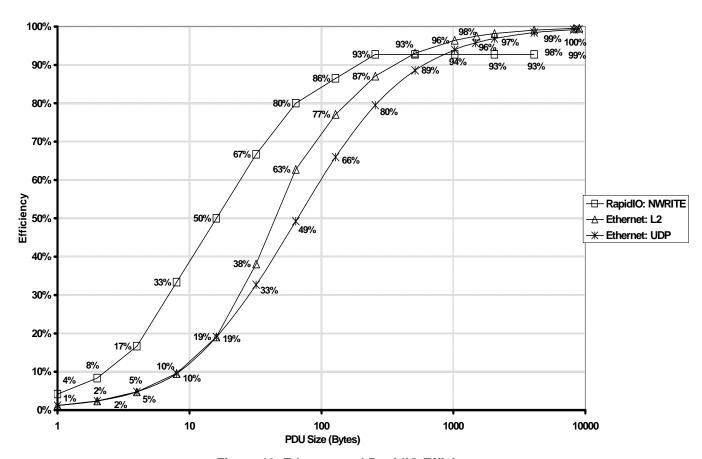

RapidIO technology is a packetized point-to-point interconnect fabric. Packets carry user payloads from 1 to 256 bytes. Both serial and parallel PHYs are defined, allowing effective data rates from 667 Mbps to 30 Gbps. RapidIO networks comprise endpoints and switches as shown in Figure 9. Endpoints source and sink packets. Switches connect more than two devices and move packets from an input to an output port. Many topologies are possible in RapidIO. Large systems often allocate one or more host processors as fabric management devices. At boot up, the host is responsible for initial system discovery and initialization. During runtime, it coordinates and monitors system-level activity and error recovery.

Figure 9. RapidIO Network

# 4.1 Original Design Goals

RapidIO was originally conceived as a next-generation front-side bus for high-speed embedded processors. The value of a front-side bus that can also function as a system-level interconnect fabric was recognized early in the specification development. The initial design goals for RapidIO technology reflect these early considerations:

- Focus on embedded control plane applications

- Scope limited to in-the-box or chassis applications in the embedded space

- Lower cost and pin count

- Limited software impact

- Simplified switches

- Protocol extensibility

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

In targeting processor-centric control plane applications first, the RapidIO protocol needed reliable transport with minimal latency. Latency is reduced by minimizing the header field sizes and arranging headers to allow early access to key state. A reliable transport dictates hardware error recovery. By focusing on embedded systems, RapidIO technology avoids backward compatibility requirements that can impose significant limitations and increase complexity. This limit in scope reduces the header overhead by reducing the size of address fields. PHY complexity is reduced by simplifying the required electrical channel. Use of either a source-synchronous parallel or embedded clock serial PHY allows higher bit rates per wire because the data and clock encounter similar propagation delays. These PHYs also reduce the width of the interconnect at a given data rate over earlier parallel shared bus interconnects. To limit the software impact, RapidIO technology retains many usage paradigms supported in bus-based protocols, such as address-based reads and writes, messaging, and doorbell interrupts. By adopting a straightforward destination-based transport model, RapidIO technology reduces switch gate count and die size by minimizing the header fields that must change as packets pass through a switch.

The RapidIO protocol is hierarchical and is designed to be layered as shown on the right in Figure 3. RapidIO headers include spare bits for future protocol extensions. Use of these spare bits is specified to allow backward compatibility in the future.

## 4.2 Protocol Overview

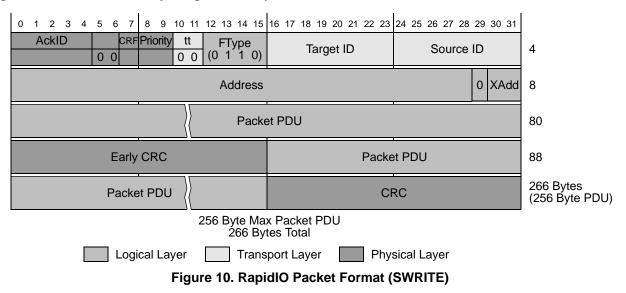

The layers of the RapidIO protocol work together to allow endpoints in a fabric to communicate. The logical layer is the highest specified layer. It defines operations such as read, write, and messaging, which are implemented using specific transaction types. The transport layer defines how logical layer request transactions are routed to their destination and how responses find their way back to the requestor. The physical layer is the lowest layer of the protocol and specifies the link protocol as well as the electricals used on the physical link. The protocol defines a discrete variable-sized packet carrying header information for each protocol layer and a data payload ranging from 1 to 256 bytes. All packets must be a multiple of 4 bytes long with padding when necessary. Figure 10 shows the packet format for an SWRITE transaction type. The 8-byte packet header is followed by write data of up to 256 bytes. The header is composed of fields defined by the protocol layers.

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

Physical layer fields appear first so that the most immediately relevant fields can be accessed first. The AckID field supports positive acknowledgement of each packet moved across a link. Priority and critical request flow (CRF) bits follow the AckID and are used by the physical layer to enforce ordering, prevent deadlock, and provide QoS features.

Transport layer fields include the tt field, which specifies the size of the TargetID and SourceID fields to define the route request and response transactions across the fabric.

The logical layer fields begin with the FType, which determines the general class of logical layer transaction. Following the transport fields are additional logical layer fields, which in this example include a target write address for the payload. The actual write data follows this address.

All packets end with a 2-byte CRC field for end-to-end error checking. To provide sufficient error coverage for payloads larger than 80 bytes, an early 2-byte CRC field is inserted. Early CRC also simplifies cut-through routing in switches by allowing the integrity of the header fields to be determined before the entire packet is received. Should a defective packet be detected, a mechanism is defined to abort the packet.

## 4.2.1 Physical Layer

The RapidIO physical layer defines how to move each packet reliably across individual links. Links consist of one or more unidirectional signals in each direction. The physical layer includes the link and PHY layers. Currently, there are two RapidIO physical layers that offer different performance, pin count, and channel (link) length options. Together, they offer effective bandwidths ranging from 667 Mbps to 30 Gbps in each direction, depending on link speed and width.

The RapidIO link protocol guarantees reliable delivery across the link and manages three tasks: link initialization, packet transmission, and error recovery. Several mechanisms are used to implement the protocol.

First, individual packets participate in the link protocol through physical layer packet header fields. The AckID and CRC fields shown in Figure 10 ensure reliable delivery of packets. Packet loss is detected because the receiver must positively acknowledge each packet received. The AckID field allows an acknowledgement to be associated with each packet sent by the transmitter.

Second, a special link layer packet type is defined. Because two independent devices exist on either side of the link, there must be a way to coordinate link operation between them. This is accomplished using a small packet called a control symbol. Control symbols are error protected using parity or CRC protection depending on the physical layer. In addition, the link protocol itself provides error protection. To minimize the loop latency of the link protocol, control symbols can be embedded within packets. Control symbols perform the following basic protocol functions depending on the physical layer used:

- Packet acknowledgement

- Packet delineation (serial PHY only)

- Link maintenance and status

- Flow control

- Idle (parallel PHY only)

Control symbols acknowledge packets by passing the AckID of the packet back to the transmitter. During normal operation, a positive acknowledgement indicates the packet was received correctly. When an error

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

is detected, an error acknowledgement is sent instead. Except for certain rare error scenarios, an error acknowledgment causes hardware to resend the packet. Therefore, hardware automatically recovers most link errors without software intervention.

Packet AckIDs are numbered sequentially as they are transmitted and must be acknowledged in order as well. As a result, loss or corruption of packets or acknowledgment control symbols can be detected when they arrive with non-sequential AckIDs. Because RapidIO packets are not of fixed size, packet boundaries must be explicitly defined in the protocol. While a dedicated interface signal is used for this purpose in the parallel PHY, control symbols are used in the serial PHY. Control symbols also signal the premature end of a packet under certain error conditions.

Control symbols are also used to initialize a link at power on or after an unrecoverable error event. In addition, they allow status to be reported across the link and recovery initiated when certain control symbol or protocol errors occur.

A RapidIO link is never idle. When no packets are available for transmission, the parallel PHY sends a continuous stream of "idle" control symbols. The serial PHY continuously transmits the IDLE sequence (a specific set of 10-bit characters).

Because control symbols are defined at the physical layer, the specific control symbol format differs between the two defined physical layers. For delimiting, both physical layers implement a 32-bit control symbol. The parallel physical layer defines a single-function control symbol, and the serial physical layer defines a more efficient dual-function symbol that can act, for example, as both a handshake and framing delimiter. There are multiple forms of link-level flow control, including receiver and transmitter-based flow control and in the future a facility to communicate congestion events to upstream queues. In addition, the parallel physical layer defines a transmission throttle mechanism.

# 4.2.2 Transport Layer

The transport layer defines how endpoints are identified within a RapidIO fabric and how packets are routed to a desired destination. In general, endpoints are the only devices in a RapidIO fabric to source and sink packets. Switches only route packets from an input port to an output port. Each endpoint is assigned a device ID to identify it within the network. Switches have no device ID and are effectively invisible in a RapidIO fabric.

RapidIO is a destination-based interconnect. All packets carry a destination ID corresponding to the device ID of the desired destination endpoint and a source ID corresponding to the device ID of the source of the packet. The source ID is used when a response is required or when errors are reported. RapidIO switches are routing-table based. When a packet arrives at the input port of a switch, the switch examines the destination ID of the packet and looks up the output port associated with that destination in its routing table. The transport layer defines 8-bit (small) and 16-bit (large) device IDs supporting respectively 256 and 64K endpoints in the network. Implementations with large device IDs must also support small device IDs. Systems must choose globally at initialization which transport size to use. Runtime operation of endpoints supporting different device ID sizes within the same fabric is outside the scope of the specification.

Because switches have no device ID, special provision is made in the logical layer maintenance transaction to target switches for discovery, initialization, and configuration. The number of links are counted along a specific path through the network, and this hop count is included in the maintenance transaction header.

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

As maintenance packets follow the path determined by their destination IDs through the network, each switch decrements the hop count field in the packet by one. When the hop count equals zero upon arrival at a switch, the switch consumes the maintenance transaction.

The specification gives wide latitude to endpoint implementations. A single RapidIO device may contain multiple RapidIO endpoints, each with its own device ID. Such a device may have one or more ports associated with those endpoints. A physical device might also contain one or more endpoints and a switch.

#### 4.2.3 **Logical Layer**

The logical layer is the highest protocol layer defined by the specification. Applications use operations defined here to move data across the interconnect fabric. The logical layer defines many operations in earlier interconnects plus additional ones helpful to embedded applications. One or more transaction types are used to implement an operation. Collectively they are divided into request and response packet types. Some requests require responses by the destination endpoint while others do not. Operations defined by RapidIO include:

- Read and writes

- Write with response

- Streaming write

- Atomic (read-modify-write)

- Messaging

- Maintenance

- Data streaming

- Globally shared memory

- Flow control

- User-defined operations

#### 4.2.3.1 **Reads and Writes**

RapidIO defines several forms of read and write operations, including byte-granularity reads and several atomic read-modify-write operations. Also defined are byte-granularity writes, a more efficient 8-byte granularity "streaming" write (format shown in Figure 10), and a write with response operation.

A variety of address sizes for read and write operations allow individual applications to minimize packet header overhead. RapidIO allows a source endpoint to address a total of 34, 50, or 66 bits of address space at the destination endpoint. The address fields are shown in Figure 10.

Reflecting its heritage as a control plane interconnect, RapidIO technology defines a variety of atomic read-modify-write transaction types that support memory semaphores. These include increment, decrement, compare-and-swap, test-and-swap, swap, set and clear. Only swap, compare-and-swap and test-and-swap require responses to the request.

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0 Freescale Semiconductor 23

## 4.2.3.2 Messaging

Messaging is a hardware-based mechanism for sending up to 4-Kbyte payloads to a remote destination. The source does not need to know the destination implementation or memory map. The specification defines the following messaging capabilities:

- Segmentation and reassembly

- Concurrent message transmission

- Multiple message priorities

RapidIO defines packet payloads up to 256 bytes; messages larger than 256 bytes are segmented into multiple message segments and reassembled at the destination even if they arrive out of order. Up to 16 multi-segment messages can be in flight between a source and destination. Each message request segment requires an end-to-end logical acknowledgement from the destination. The destination may respond with retry should hardware be temporarily unable to process the packet.

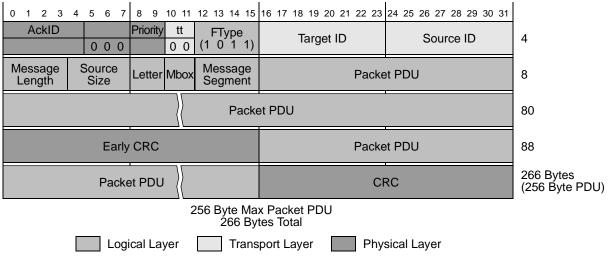

Figure 11 shows the format of a MESSAGE request packet. No addresses are carried by a message transaction. The location in memory of source and destination data is defined locally to the endpoint.

Figure 11. RapidIO Packet Format (MESSAGE)

RapidIO does not define a programming model or specific hardware implementation for messaging. Existing implementations consist of one or more hardware-managed queues at the source and destination. Upper layer services needing to send a message queue one or more messages in memory for transmission. Hardware reads a message from the queue, segments it when necessary, and issues the transactions to the interface for transmission. At the destination, hardware reassembles the segments into a memory-based queue structure and when complete notifies software.

### 4.2.3.3 Maintenance

As with many other interconnects, RapidIO defines a separate address space for accessing initialization, status, and configuration registers. There is an 8 Mbyte address space with regions allocated for required and implementation-specific registers. Maintenance read and write operations are fully acknowledged and implemented with a single distinct transaction type that supports both requests and associated responses.

System Interconnect Fabrics: Ethernet Versus RapidIO® Technology, Rev. 0

This transaction type also implements the maintenance port-write. Because RapidIO switches do not have associated DeviceIDs, they cannot initiate normal transaction types to report errors or status. This transaction type has no response and is not guaranteed to be delivered because it may be dropped by the target endpoint.

## 4.2.3.4 Data Streaming

Relatively new to the specification are operations targeting data plane applications. Data streaming allows many different protocols to be encapsulated and transported concurrently across a RapidIO fabric. The encapsulation operation itself is protocol-independent and supports up to 64 Kbyte protocol data units (PDUs) using segmentation and reassembly hardware. Hundreds of traffic classes and thousands of streams of data can be identified between a given pair of endpoints so that concurrent transmission of multiple PDUs between endpoints is permitted.

## 4.2.3.5 Globally Shared Memory

RapidIO defines cache coherence and OS support operations that allow RapidIO to act as a coherent fabric for multiprocessor cache-coherent non-uniform memory access (ccNUMA) systems. These operations allow a processing device with a cache to keep its cache state coherent with others in the fabric. I/O devices can then request data that is coherent with system caches. Other functions allow remote management of processor translation lookaside buffers (TLBs).

## 4.2.3.6 Logical Level Flow Control

To reduce congestion within a fabric, a flow control facility is defined in the logical layer. This capability allows destination endpoints or fabric switches to shut off traffic from a specific source endpoint. This XON/XOFF messaging protocol applies to traffic within a specific logical flow. Soon, the specification will include additional end-to-end traffic management facilities, such as the ability to control the flow of thousands of individual traffic streams.

# 4.2.3.7 Logical Layer Ordering

Logical layer operations do not require packets to be transported in order across the fabric for proper operation. Where ordering must be restored at the destination, tagging fields in the packet header are used. However, many higher-level services require ordering, so the logical layer defines prioritized flows. Flows are an ordered sequence of request transactions between a single source and destination endpoint pair. Traffic between unrelated pairs of endpoints is unordered with respect to each other. The logical layer defines a set of ordering rules that are implemented and enforced at the physical layer.

Multiple transaction request flows between a given endpoint pair are defined. These flows are given a FlowID. Flows are labeled alphabetically A, B, C, and so on starting with A. Flows in RapidIO fabric are prioritized with flow A as the lowest priority. As they traverse the fabric, transactions that are part of a higher-priority flow between a pair of endpoints can pass transactions in a lower-priority flow. To avoid deadlock, transactions in a lower-priority flow must never pass those of a flow with the same or a higher priority. Within a flow, the logical layer specifies the same ordering rules for read and write requests that are common to many applications. Destination endpoints must complete write requests in the same order

System Interconnect Fabrics: Ethernet Versus RapidIO<sup>®</sup> Technology, Rev. 0

they were issued at the logical layer of the source. Read requests must push all earlier writes to completion at the destination endpoint. Responses are not part of any flow and are unordered with respect to requests that did not generate them as well as any other responses. Maintenance transactions exist outside of request flows or responses and are prioritized. Higher-priority maintenance packets can pass lower-priority ones taking the same path through the fabric.

# 4.3 Priority, Deadlock Avoidance, and Buffer Management

Deadlock avoidance in any system entails avoiding dependency loops. In a RapidIO system, these loops exist when logical layer operations require a response. For example, read transactions introduce the possibility of a dependency loop. When the entire loop between two endpoints is filled with read requests, specific deadlock avoidance measures are needed to ensure that responses to outstanding reads can complete and release their resources.

The logical layer defines prioritized request flows and associated ordering rules. Each packet has a 2-bit physical layer priority field and an optional Critical Request Flow (CRF) bit in the header. By assigning each packet to physical layer priorities, logical flows are identified, ordering rules are enforced, and deadlocks avoided.

Defining priorities at the physical layer greatly simplifies switches because, with the exception of maintenance transactions, there is no need to know the packet transaction type or its interdependency with other packets when making switching decisions. Ordering decisions are based only on the packet source ID, destination ID, and priority bits.

Assigning responses a higher priority than the associated request allows responses to make forward progress in the system. The physical layer requires switches and endpoints to implement mechanisms that allow higher-priority packets (and therefore associated responses) to make forward progress in the system. Table 3 shows the mapping of the four priorities to logical layer flows and their associated requests and responses. Note that the priority of a request packet defines its logical flow. Because each request flow must have its response assigned to a higher priority, up to three logical flows (A, B, and C) can be accommodated.

| Overall Physical Priority | Flow A   | Flow B   | Flow C   |  |

|---------------------------|----------|----------|----------|--|

| PRIO Field                | FIOWA    | FIOW B   |          |  |

| 3                         | Response | Response | Response |  |

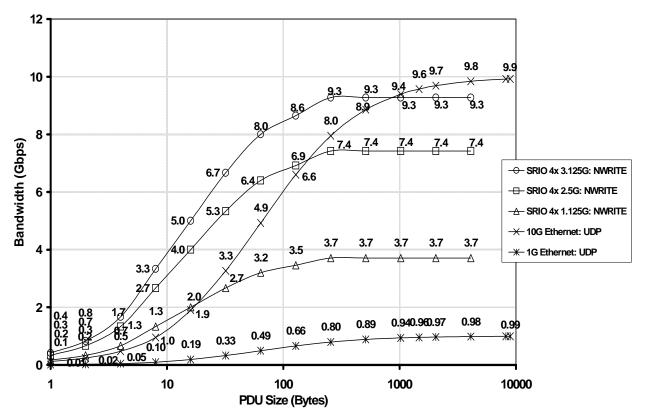

| 2                         | Response | Response | Request  |  |