# 32-Bit automotive MCUs

## MAC57D5xx DIS MCUs for Automotive Instrument Clusters

The MAC57D5xx family is the next-generation platform of instrument cluster devices specifically targeted to the cluster market using single and dual high-resolution displays.

#### **TARGET APPLICATIONS**

- ▶ Instrument clusters

- ▶ Heads-up display

- ▶ Multifunction display

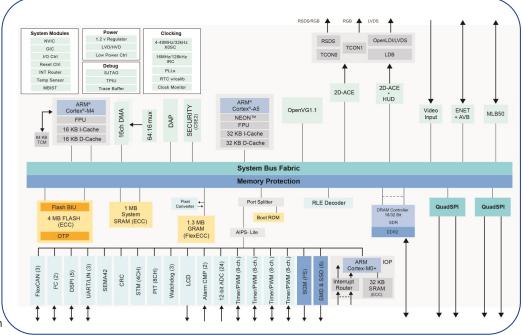

Leveraging a highly successful MPC56xxS product family, we are introducing a multicore architecture powered by ARM® Cortex®-M (for real-time applications) and ARM Cortex-A processors (for applications and HMI), coupled with 2D graphics accelerators, a head-up display (HUD) warping engine, dual TFT display drive, integrated stepper motor drivers and a powerful I/O processor that will offer leading-edge performance and scalability for cost-effective applications.

This family supports up to two WVGA resolution displays, including one with in-line HUD hardware warping. Graphics content is generated using a powerful Vivante 2D graphics processing unit (GPU) supporting OpenVG1.1, and the 2D animation and composition engine (2D-ACE), which significantly reduces memory footprint for content creation.

Embedded memories include up to 4 MB flash, 1 MB SRAM with error correcting codes (ECC) and up to 1.3 MB of graphics SRAM without ECC. Memory expansion is available through DDR2 and SDR DRAM interfaces while two flexible QuadSPI modules provide SDR and DDR serial flash expansion.

In response to the growing desire for security and functional safety, the MAC57D5xx family integrates our latest SHE-compliant cryptographic services engine (CSE2) and delivers support for ISO26262 ASIL-B functional safety compliance.

#### **FEATURES**

Cortex-A5, 32-bit CPU (Application processor)

- ▶ Floating point unit (FPU) supporting double-precision floating-point operations

- ▶ NEON ™ Media Processing Engine

- ▶ Memory management unit

- ▶ Up to 320 MHz

#### Cortex-M4, 32-bit CPU

#### (Vehicle processor)

- ► 64 KB tightly-coupled memory (TCM)

- Single precision FPU

- Up to 160 MHz

### Cortex-M0+, 32-bit CPU (I/O processor)

- Intelligent stepper motor drive

- Low-power mode peripheral management

#### **Memory Sub-system**

- System memory protection unit

- 4 MB on-chip flash including small sectors for EEPROM

- ▶ 1 MB on-chip SRAM with ECC

- 1.3 MB on-chip graphics SRAM with FlexECC

#### **Expandable Memory Interfaces**

- 2 x Dual QuadSPI serial flash controllers (including HyperFlash™ support)

- Supports SDR and DDR serial flash

- DRAM controller supporting SDR and DDR2

#### **Graphics Features**

- Vivante GC355 GPU supporting OpenVG™ 1.1

- 2 x 2D-ACE display controllers supporting up to 2 x WVGA displays

- In-line hardware HUD warping engine

- ▶ Digital RGB, TCON0 (RSDS), TCON1

- and OpenLDI/LVDS output options

- Digital video input

- RLE decoder for memory-memory decompression

#### **Safety and Security**

- Latest CSE2 security—Secure Boot,

Secure Mileage and Component

Protection

- ▶ ISO 26262 ASIL-B Compliant MCU

#### MAC57D5xx BLOCK DIAGRAM

#### **Peripherals**

- 6 Stepper Motor Drivers with patented Stall Detection technology

- ➤ ound Generator Module (SGM) with PWM and I<sub>2</sub>S outputs

- Autonomous RTC (self calibrating)

- ▶ Rich set of communication peripherals, including Ethernet-AVB, MLB50, CAN, LIN, SPI, l₂C

- Up to 32 Timer/PWM channels

- ▶ 12-bit ADC and Analogue Comparators

#### **Key Electrical Characteristics**

▶ -40 °C to +105 °C (ambient)

#### **Package Options**

▶ 516 MAPBGA, 208 LQFP, 176 LQFP

#### Tools

- Debugger: Green Hills Probe, Lauterbach, IAR™

- Multicore compiler: ARM, Green Hills

#### MAC57D5xx FAMILY MATRIX

| Family    | Flash | SRAM                                         | Package    | SDR                | DDR2                      | Quad SPI                                           | GPU               |

|-----------|-------|----------------------------------------------|------------|--------------------|---------------------------|----------------------------------------------------|-------------------|

| SAC57D54H | 4 MB  | 1.3 MB (non<br>ECC)/ 2 x 512<br>kbit (w/ECC) | 208 LQFP   | 16-bit,<br>160 MHz | None                      | 2 x Dual SDR/DDR<br>QuadSPI, 100 MHz<br>(200 MB/s) | GC355<br>(OpenVG) |

|           |       |                                              | 516 MAPBGA |                    | 16- or 32-bit,<br>320 MHz |                                                    |                   |

| SAC57D53H | 3 MB  | 1.3 MB (non<br>ECC)/ 2 x 512<br>kbit (w/ECC) | 208 LQFP   | 16-bit,<br>160 MHz | None                      | 2 x Dual SDR/DDR<br>QuadSPI, 100 MHz<br>(200 MB/s) | GC355<br>(OpenVG) |

|           |       |                                              | 516 MAPBGA |                    | 16- or 32-bit,<br>320 MHz |                                                    |                   |

| SAC57D52L | 2 MB  | 1.3 MB (non<br>ECC)/ 2 x 512<br>kbit (w/ECC) | 208 LQFP   | 16-bit,<br>160 MHz | None                      | 2 x Dual SDR/DDR<br>QuadSPI, 100 MHz<br>(200 MB/s) | GC355<br>(OpenVG) |

$<sup>\</sup>hbox{\ensuremath{^{**}}Not all feature differences shown in table above, refer to datasheet for specific feature details}$

### www.nxp.com/MAC57D5xx

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. © 2016 NXP B.V.