10/2000 Rev. 2.1

# Addendum to MPC860 PowerQUICC™ User's Manual MPC860P, MPC850SAR and MPC855T AAL2 Microcode Specification

This supplement to the MPC860 PowerQUICC<sup>TM</sup> User's Manual describes the features of a microcode package that implements the ATM adaptation layer type 2 (AAL2) on the MPC860P, the MPC850SAR, and the MPC855T. The MPC860 PowerQUICC<sup>TM</sup> User's Manual, the MPC8xx ATM Supplement to the MPC860/MPC850 PowerQUICC<sup>TM</sup> User's Manual, and the MPC860P Supplement to the MPC860 PowerQUICC<sup>TM</sup> User's Manual should be consulted for any features not described in this document.

To locate any published errata or updates for this document, refer to the website at http://www.mot.com/netcomm.

#### 1.1 AAL2 Features and Restrictions

Features of the AAL2 microcode are as follows:

- Implements the ITU I363.2 specification

- Runs on the communications processor (CP) of the MPC860P, the MPC850SAR, and the MPC855T

- Supports up to 224 AAL2 channels. Channel numbers 32–255 are available for AAL2. Channels 0-31 and channel numbers greater than 255 can be used for non-AAL2 channels.

- The microcode is executed internally from dual-port RAM.

- Built-in mechanism for Timer CU support without host intervention

- After the host initializes the AAL0 BDs and buffers associated with the AAL2 channels, the AAL2 microcode handles the interface with AAL0 operation.

- Optional masking of the APC overrun (APCO) event

- Optional enabling of RISC timers when using the timer CU mechanism

- Reassembly:

- Sequence number (SN) and parity check for each CPS-Packet

- Length indication (LI) and CRC5 check for each cell

- OSF of the STF check (valid value is less than 48)

- Segmentation:

- Perform CPS-PDU padding as needed

- Sequence number (SN) and parity generation for each cell

- CRC5 generation for the CPS-PH

The following restrictions apply when the AAL2 microcode is used:

- Serial ATM is not available on SCC4. (UTOPIA can still be used.)

- AAL0 buffers should start on a 64-byte-aligned address.

- DSP functionality is not available.

- No other microcode RAM packages or patches can be used.

#### 1.2 Overview of the AAL2 Microcode

The AAL2 microcode package implements the ITU I.363.2 specification. The AAL2 microcode builds upon AAL0 operation (AAL0 microcode in ROM) and existing ATM data structures, such as connection tables. For each AAL2 channel, the AAL2 microcode converts data from AAL2 packets into AAL0 cells and vice versa. After initialization, the AAL0 operation is transparent to the AAL2 host application.

Table 1-1 lists acronyms and abbreviations used in this document.

Table 1-1. Acronyms and Abbreviated Terms

| Term              | Meaning                                                                                                                                                                               |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8xxSAR            | Represents the MPC860P, MPC850SAR or MPC855T                                                                                                                                          |

| AAL2 channel      | The logical connection through which ATM communicates. Each channel corresponds to a specific VPI/VCI combination. The channel can also be called a VCC (virtual channel connection). |

| AAL2_CT           | AAL2 connection table. Each active AAL2 channel has a connection table consisting of an AAL2_RCT and AAL2_TCT.                                                                        |

| AAL2_RCT          | AAL2 receive connection table (one RCT for each AAL2 channel)                                                                                                                         |

| AAL2_Rx_Queue     | Queue of RPDs (functionally equivalent to an RxBD table)                                                                                                                              |

| AAL2_TCT          | AAL2 transmit connection table (one TCT for each AAL2 channel)                                                                                                                        |

| AAL2_Tx_Queue     | Queue of TPDs (functionally equivalent to a TxBD table)                                                                                                                               |

| AAL2_TxWait_table | The wait table used to implement the Timer CU mechanism                                                                                                                               |

| AAL2_TxWait_PTR   | The wait pointer marking expired active buffers for the Timer CU mechanism                                                                                                            |

| Active BD         | AAL0 BD that points to the active buffer                                                                                                                                              |

Table 1-1. Acronyms and Abbreviated Terms (Continued)

| Term                  | Meaning                                                                                                                                                             |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active buffer         | The next AAL0 buffer to be processed (or the buffer currently being processed) by the AAL2 microcode. The active buffer may be empty or partially filled.           |

| APC                   | ATM pace control for scheduling transmission of cells                                                                                                               |

| CPS-Packet            | Common parts sublayer packet format for AAL2 data as defined in the ITU I.363.2 specification. A packet consists of a packet header (PH) and a packet payload (PP). |

| DPR                   | Dual-port internal RAM of the 8xxSAR. The AAL2 microcode is located here.                                                                                           |

| Host                  | The user's AAL2 application running on the PowerPC core of 8xxSAR                                                                                                   |

| μs                    | Microseconds                                                                                                                                                        |

| ms                    | Milliseconds                                                                                                                                                        |

| OSF                   | Offset field                                                                                                                                                        |

| Partially filled cell | An ATM cell (AAL0 buffer) which is not completely filled with CPS-Packets                                                                                           |

| RPD                   | Receive packet descriptor. Describes the CPS-Packet for receiving (similar to an RxBD)                                                                              |

| Rx                    | Receive (Data direction is toward the 8xxSAR.)                                                                                                                      |

| STF                   | Start field                                                                                                                                                         |

| Timer CU              | The timer (combined use) mechanism to limit the time allowed for filling partially filled cells                                                                     |

| TPD                   | Transmit packet descriptor. Describes the CPS-Packet for transmitting (similar to a TxBD)                                                                           |

| Tx                    | Transmit (Data direction is away from the 8xxSAR.)                                                                                                                  |

#### 1.2.1 AAL2 Transmit Overview

The host generates CPS-Packets with each packet consisting of a CPS-PH (CPS packet header) and CPS-PP (CPS packet payload). The HEC field in the CPS-PH is generated by the AAL2 microcode.

For each CPS-Packet to be sent, the host prepares a TPD and adds it to the AAL2\_Tx\_Queue of the AAL2 channel. Similar to a TxBD, a TPD contains control information and the pointer to the CPS-Packet.

For each AAL2 channel, the AAL2 microcode prepares AAL0 buffers for transmission. Each AAL0 buffer consists of a 4-byte header and 48-byte payload. Ready AAL0 buffers packed with AAL2 channels are transmitted (along with other ATM channels) by the 8xxSAR according to the APC scheduling. Note that the ATM host command APC BYPASS can also be used for direct scheduling of AAL2 channels.

For each AAL2 channel, the host should set the I bit in the associated AAL0 TxBDs so that after each cell transmission is completed, the 8xxSAR attempts to generate an interrupt to the host. However, the interrupt does not reach the host because trap hardware intercepts the interrupt at the beginning of the service routine. This is the activation mechanism for the AAL2 microcode to attempt to pack ready CPS-Packets from the channel's AAL2\_Tx\_Queue into an available AAL0 buffer. Note that the first time the AAL2 microcode is activated (and whenever the host or APC unit attempts to transmit a cell when the buffer is not ready), an idle cell is sent.

For each active AAL0 buffer, the AAL2 microcode transmitter does the following:

- Copies the 4-byte cell header from the channel's AAL2\_TCT

- Generates the STF field of the CPS-PDU

- Fills the payload (CPS-PDU) with CPS-Packets

- If the AAL2 microcode packs the whole CPS-Packet into the AAL0 buffer, it marks the TPD as available (R=0). If TPD[INT] is set and the interrupt is not masked by AAL2\_TCT[TPI], the AAL2 microcode adds an entry to the exception queue (with the AAL2 bit and TXB bit set) to signal the host that this CPS-Packet has been processed. The global interrupt count (INT\_CNT) is also decremented. If INT\_CNT reaches zero, the global interrupt (GINT) bit in the event register is set and an interrupt is generated to the host. (The INT\_CNT is then restored to the INT\_ICNT value.) If the exception queue is already full, the microcode sets the IQOV bit in the event register—entries in the exception queue are not overwritten. The host may then service the exception queue and process the appropriate AAL2\_Tx\_Queues by filling available CPS-Packets and marking their TPDs as ready (R=1).

- If the AAL2 microcode cannot pack the whole CPS-Packet into the active buffer (because the AAL0 buffer became full), the current CPS-Packet parameters are stored in the AAL2\_TCT. The next time the AAL2 microcode is activated to service this channel (to fill a new active AAL0 buffer), it resumes operation from where it stopped.

- Generates the HEC field for each CPS-PH

- If the active buffer is filled with CPS-Packets, its TxBD[R] is set so that the AAL0 microcode will process it for actual transmission.

Note that the host application does not interface directly with the AAL0 buffers. The host interfaces with the AAL2 microcode, which in turn interfaces with the AAL0 transfer mechanism of the 8xxSAR.

AAL2 microcode provides a built-in Timer CU mechanism which makes sure that CPS-Packets in partially filled AAL0 buffers are not delayed by the AAL2 microcode more than a fixed time. The host can program the maximum delay for each channel in the AAL2\_TCT.

If there are not enough ready CPS-Packets in the AAL2\_Tx\_Queue of this channel to fill the (partially filled) active buffer, the AAL2 microcode temporarily stores the buffer's parameters in the AAL2\_TCT. If the Timer CU mechanism is enabled for this channel, the Timer CU count down for this AAL2 channel is also started. If the Timer CU counter expires before the active buffer becomes full, the AAL2 microcode activates in order to pad the buffer with zeros and mark its BD as ready. This buffer (along with other ready AAL0 buffers of the channel) is then transmitted in a separate process by the 8xxSAR according to the APC scheduling or host scheduling (using APC BYPASS).

If the AAL2 microcode is activated to process a channel's partially filled active buffer before its Timer CU counter expired, the active buffer is filled with CPS-Packets, the active BD is closed (R bit is set) and the channel's Timer CU counter is deactivated. However, if the active buffer is still not full, the Timer CU counter continues its count down.

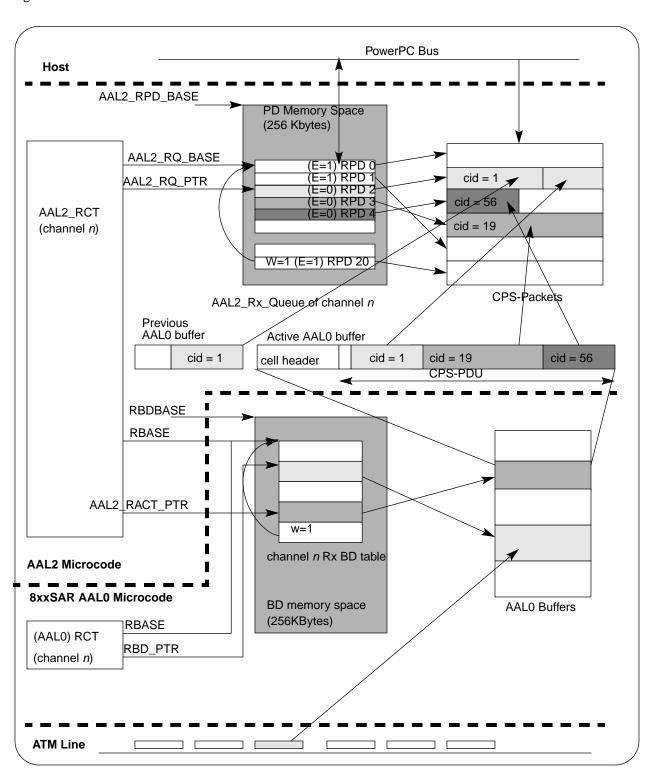

#### 1.2.2 AAL2 Receive Overview

The 8xxSAR receives AAL0 cells and places them in the external memory. Because all of the RxBDs associated with AAL2 channels have the I bit set (like the TxBDs), the 8xxSAR attempts to generate an interrupt to the host. However, trap hardware intercepts the interrupt at the beginning of the service routine and activates the AAL2 microcode.

For each activation, the AAL2 microcode receiver processes one active AAL0 buffer. The AAL2 microcode does the following:

- Checks the STF field of the CPS-PDU

- Breaks the CPS-PDU into CPS-Packets

- Verifies the HEC for each CPS-PH

- Copies each CPS-Packet to external memory according to the pointer in the current RPD of the channel's AAL2 Rx Queue

- Checks the CPS-PDU for errors. If an error is detected, an indication is written to the associated RPD and the CPS-Packet is discarded. See Section 1.5.1, "Receive Packet Descriptor (RPD)," for a description of the possible errors.

- If a complete CPS-Packet is retrieved from the active buffer, the AAL2 microcode marks the RPD as available to the host (E = 0). If RPD[INT] is set and the interrupt is not masked by AAL2\_RCT[RPI], the AAL2 microcode adds an entry to the exception queue (with the AAL2 bit and RXB bit set) to signal the host that a CPS-Packet has been received. The global interrupt count (INT\_CNT) is also decremented. If INT\_CNT reaches zero, the global interrupt (GINT) bit in the event register is set and an interrupt is generated to the host. (The INT\_CNT is then restored to the INT\_ICNT value.) If the exception queue is already full, the microcode sets the IQOV bit in the event register—entries in the exception queue are not overwritten. The host may then service the exception queue and process the appropriate AAL2\_Rx\_Queues and mark their RPDs as empty (E=1).

- If only a partial CPS-Packet is retrieved from the AAL0 buffer, the AAL2 microcode stores the CPS-Packet parameters in the channel's AAL2\_RCT. When the AAL2 microcode is next activated to serve this channel (after a new cell has been placed in an AAL0 buffer), it resumes operation from where it stopped.

- If the complete AAL0 buffer is processed, its BD is marked empty. If, however, the AAL2 microcode could not finish processing the AAL0 buffer (because there are not enough available RPDs in the AAL2\_Rx\_Queue), the AAL2 microcode discards the CPS-PDU and adds an entry to the exception queue (with the AAL2 bit and OVF bit set) to indicate an AAL2\_Rx\_Queue overflow.

If the 8xxSAR attempts to receive a cell, but there is no available AAL0 buffer (the next RxBD of the channel is not empty), the 8xxSAR generates an exception entry with a BSY indication. Because this indication is directly related to AAL0 operation, the AAL2 bit in the exception entry is not set. This type of exception indicates that the AAL2 microcode is too slow to process the AAL0 buffers that were received previously by the 8xxSAR. The system load could be so great that the AAL2 microcode cannot maintain the data rate. Also, the channel's RxBD table could be too small; that is, the latency of the AAL2 microcode in processing the active buffers is greater than the delay tolerance provided by the RxBD table. The host should reconfigure the system to prevent such exceptions.

#### 1.3 AAL2 Microcode Interface with the Host

The host application interacts with the AAL2 microcode using packet descriptors (PDs) placed in queues. Inside each queue, the PDs are processed first in first out (FIFO). Each AAL2 channel has one transmit queue (AAL2\_Tx\_Queue) and one receive queue (AAL2\_Rx\_Queue).

The transfer of control between the host and the AAL2 microcode is managed through the ready bit (R) in the TPD and the empty bit (E) in the RPD. This is the same mechanism used for SCC TxBDs and RxBDs except that the ATM exception queue is used instead of an event register to signal when the microcode is ready to transfer control back to the host.

A TPD with R=0 (not ready for transmission) is available to the host. The AAL2 microcode processes a TPD and its packet only after the host has set TPD[R]. The microcode then clears TPD[R] after processing the packet and can signal the host by adding an entry in the exception queue.

An RPD with E=0 (not empty) is available to the host. The AAL2 microcode uses a RPD to retrieve a packet only after the host has set RPD[E]. The microcode then clears RPD[E] after retrieving the packet and can signal the host by adding an entry in the exception queue.

#### 1.4 AAL2 Microcode Data Structures for Transmit

This section describes the AAL2 microcode's data structures used for transmitting AAL2 packets.

#### 1.4.1 Transmit Packet Descriptor (TPD)

Similar to buffer descriptors, each transmit packet descriptor (TPD), shown in Figure 1-1, contains control bits and the pointer to the CPS\_Packet. However, the TPD does not contain status bits. The status feedback from the CP is given through the exception queue; see Section 1.9, "AAL2 Microcode Exceptions." The host should program all TPD fields during initialization.

|            | 0 | 1      | 2 | 3   | 4 | 5 | 6 | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|------------|---|--------|---|-----|---|---|---|----|---|---|----|----|----|----|----|----|

| Offset + 0 | R | _      | w | INT | _ | _ | _ | СМ | _ | _ | _  | _  | _  | _  | _  | _  |

| Offset + 2 |   | _      |   |     |   |   |   |    |   |   |    |    |    |    |    |    |

| Offset + 4 |   | TP_PTR |   |     |   |   |   |    |   |   |    |    |    |    |    |    |

| Offset + 6 |   |        |   |     |   |   |   |    |   |   |    |    |    |    |    |    |

Figure 1-1. Transmit Packet Descriptor (TPD)

Table 1-2 describes the TPD fields.

**Table 1-2. TPD Field Descriptions**

| Offset | Bits | Name | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00   | 0    | R    | Ready. Determines whether the CPS-Packet is ready for transmission.                                                                                                                                                                                                                                                                                                                          |

|        |      |      | 0 - The CPS-Packet associated with this TPD is not ready for transmission. Host is free to manipulate the TPD or its associated CPS-Packet.                                                                                                                                                                                                                                                  |

|        |      |      | 1 - The CPS-Packet associated with this TPD has not been packed or currently is packed into the active AAL0 buffer. Host may not write into this TPD or its associated CPS-Packet once this bit is set.                                                                                                                                                                                      |

|        |      |      | Host sets this bit after the CPS-Packet associated with this TPD is ready for transmission. AAL2 microcode clears this bit after the CPS-Packet has been packed into the active AAL0 buffer. During initialization, the host should clear the ready bit in all TPDs.                                                                                                                         |

| 0x00   | 1    | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                 |

| 0x00   | 2    | w    | Wrap. Determines whether this is the last TPD in the AAL2_Tx_Queue.                                                                                                                                                                                                                                                                                                                          |

|        |      |      | 0 - This is not the last TPD in the AAL2_Tx_Queue.                                                                                                                                                                                                                                                                                                                                           |

|        |      |      | 1 - This is the last TPD in the AAL2_Tx_Queue. After the CPS-Packet associated with this TPD is packed into the active AAL0 buffer, the AAL2 microcode returns to the beginning of the queue (using the TPD pointed to by AAL2_TQ_BASE). The number of TPDs in the queue is programmable and is determined only by the W bit and the 256 KBytes of memory allocated for the transmit queues. |

|        |      |      | Host writes this field during initialization. AAL2 microcode does not modify this field.                                                                                                                                                                                                                                                                                                     |

| 0x00   | 3    | INT  | Determines whether interrupt is generated after this CPS-Packet is packed into the AAL0 buffer.                                                                                                                                                                                                                                                                                              |

|        |      |      | 0 - No interrupt is generated after this CPS-Packet has been packed                                                                                                                                                                                                                                                                                                                          |

|        |      |      | 1 - After the CPS-Packet is packed (and if AAL2_TCT[TPI] is set), the AAL2 microcode adds an entry to the exception queue with the AAL2 bit and TXB bit set. The global interrupt count (INT_CNT) is decremented. If the counter reaches zero, SCCE[GINT] or IDSR1[GINT] is set, and an interrupt is generated to the host.                                                                  |

|        |      |      | Host writes this field during initialization. AAL2 microcode does not modify this field.                                                                                                                                                                                                                                                                                                     |

| 0x00   | 4-6  | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                 |

**Table 1-2. TPD Field Descriptions (Continued)**

| Offset | Bits | Name   | Description                                                                                                                                                           |

|--------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00   | 7    | СМ     | Continuous mode. Determines whether the CPS-Packet associated with this TPD is marked as available to the host (R = 0) after processing by the CP.                    |

|        |      |        | 0 - Normal operation.                                                                                                                                                 |

|        |      |        | 1 - The R bit is not cleared after the TPD is closed, allowing the associated CPS-Packet to be automatically retransmitted the next time the CP accesses this TPD.    |

|        |      |        | Host writes this field during initialization. AAL2 microcode does not modify this field.                                                                              |

| 0x00   | 4-15 | _      | Reserved, should be cleared.                                                                                                                                          |

| 0x02   | 0–15 | _      | Reserved, should be cleared.                                                                                                                                          |

| 0x04   | 0–31 | TP_PTR | Transmit CPS-Packet pointer. TP_PTR points to the beginning of the CPS-Packet which reside in external memory. TPD pointer must be burst aligned (TP_PTR[28–31] = 0). |

|        |      |        | Host writes this field during initialization. AAL2 microcode does not modify this field.                                                                              |

#### 1.4.2 AAL2\_Tx\_Queue

Similar to a TxBD table, a channel's AAL2\_Tx\_Queue consists of a circular table of TPDs. AAL2\_Tx\_Queue parameters are defined in each channel's AAL2\_TCT. The queue pointer (AAL2\_TQ\_PTR) is advanced by the AAL2 microcode.

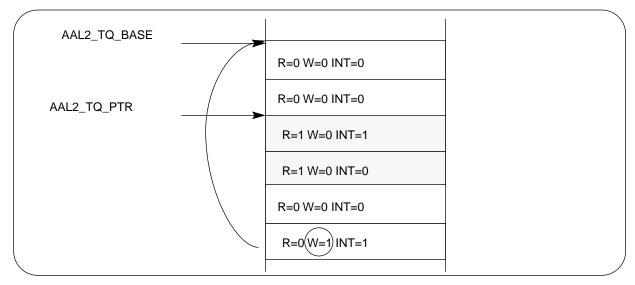

Figure 1-2 shows an example AAL2\_Tx\_Queue with six TPDs. The third and fourth TPDs (shaded) are ready for transmission (R=1). Because the INT bits are set in the third and sixth TPDs, the AAL2 microcode will generate an interrupt to the host each time a CPS-Packet associated with these TPDs has been packed.

Figure 1-2. AAL2\_Tx\_Queue Example

#### 1.4.3 AAL2 Transmit Connection Table (AAL2\_TCT)

Each channel's AAL2\_TCT, shown in Figure 1-3, contains all the parameters used by the AAL2 microcode to pack the channel's CPS-Packets. The host should configure all AAL2\_TCT fields during initialization.

|                            | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|----------------------------|---------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| CH <i>n</i> AAL2_CT + 0x20 | TPI ET SU TBM TXM -                   |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH <i>n</i> AAL2_CT + 0x22 | TBASE                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH <i>n</i> AAL2_CT + 0x24 | - TCU                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH <i>n</i> AAL2_CT + 0x26 | AAL2_TACT_PTR                         |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH <i>n</i> AAL2_CT + 0x28 | AAL2_TQ_BASE                          |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH n AAL2_CT + 0x2A        | AAL2_TQ_PTR                           |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH n AAL2_CT + 0x2C        | CLIFAD                                |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH n AAL2_CT + 0x2E        | CHEAD                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH <i>n</i> AAL2_CT + 0x30 | Reserved                              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| •                          | ' '                                   |  |  |  |  |  |  |  |  |  |  |  |  |  |

| CH n AAL2_CT + 3E          | Reserved                              |  |  |  |  |  |  |  |  |  |  |  |  |  |

Figure 1-3. AAL2 Transmit Connection Table

Table 1-3 describes the AAL2 TCT fields.

**Table 1-3. AAL2 Transmit Connection Table Field Descriptions**

| Offset | Bits      | Name  | Description                                                                                                                                                                                                         |

|--------|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x20   | 0-2       | _     | Reserved, should be cleared.                                                                                                                                                                                        |

|        | 3         | TPI   | Transmit packet interrupt. This bit controls whether the AAL2 microcode generates an interrupt to the host after processing a TPD in which the INT bit set.  0 - Interrupt generation based on INT bit is disabled. |

|        |           |       | 1 - Interrupt generation based on INT bit is enabled.                                                                                                                                                               |

|        |           |       | Host writes this field. AAL2 microcode does not modify this field.                                                                                                                                                  |

|        | 4-5       | _     | Reserved, should be cleared.                                                                                                                                                                                        |

|        | 6         | ET    | Enable Timer CU mechanism for this channel.                                                                                                                                                                         |

|        |           |       | 0 - Timer CU mechanism for this channel is disabled.                                                                                                                                                                |

|        |           |       | 1 - Timer CU mechanism for this channel is enabled.                                                                                                                                                                 |

|        |           |       | Host writes this field. AAL2 microcode does not modify this field.                                                                                                                                                  |

|        | 7         | SU    | Start-up bit. Indicates to the AAL2 microcode that this is the first time this TCT has been accessed. (The AAL2 microcode clears this bit.)                                                                         |

|        |           |       | The host must set this field during initialization.                                                                                                                                                                 |

|        | 8-9       | _     | Reserved, should be cleared.                                                                                                                                                                                        |

|        | 10        | ТВМ   | AAL2 TBSY interrupt mask. This bit allows the user to mask the AAL2 TBSY interrupt (AAL2 = 1 and TBSY = 1 in the exception queue entry).                                                                            |

|        |           |       | 0 - AAL2 TBSY interrupt is disabled. Exception entry with AAL2 and TBSY indication will not be generated.                                                                                                           |

|        |           |       | 1 - AAL2 TBSY interrupt is enabled.                                                                                                                                                                                 |

|        |           |       | Host writes this field. AAL2 microcode does not modify this field.                                                                                                                                                  |

|        | 11-<br>13 | _     | Reserved, should be cleared.                                                                                                                                                                                        |

|        | 14        | TXM   | AAL2 TXB interrupt mask. This bit allows the user to mask the AAL2 TXB interrupt (AAL2 = 1 and TXB = 1 in the exception queue entry).                                                                               |

|        |           |       | 0 - AAL2 TXB interrupt is disabled. Exception entry with AAL2 and TXB indication will not be generated.                                                                                                             |

|        |           |       | 1 - AAL2 TXB interrupt is enabled.                                                                                                                                                                                  |

|        |           |       | Host writes this field. AAL2 microcode does not modify this field.                                                                                                                                                  |

|        | 15        | _     | Reserved, should be cleared.                                                                                                                                                                                        |

| 0x22   | -         | TBASE | Transmit BD base. Holds the pointer to the first BD in the AAL0 BD table of this channel. TBASE represents bits [14–29] of an offset from TBDBASE. Bits [30–31] are always 00.                                      |

|        |           |       | This field should be the same value programmed in the TBASE as defined in the AAL0 TCT of this channel. TBDBASE is defined in the AAL0 parameter RAM of the SCC that runs this AAL2 channel.                        |

|        |           |       | Host writes this field during initialization. AAL2 microcode does not modify this field.                                                                                                                            |

Table 1-3. AAL2 Transmit Connection Table Field Descriptions (Continued)

| Offset         | Bits | Name          | Description                                                                                                                                                                                                                                                     |

|----------------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x24           | 0-7  | _             | Reserved, should be cleared.                                                                                                                                                                                                                                    |

|                | 8-15 | TCU           | Determines the maximum wait time of CPS-Packets for this channel. The wait time is defined in units of RISC timer ticks (as defined in RCCR[TIMEP]).                                                                                                            |

|                |      |               | If the user uses the Timer CU mechanism (ET=1), the TCU field should be in the range of 1-255                                                                                                                                                                   |

|                |      |               | Host writes this field during initialization. AAL2 microcode does not modify this field.                                                                                                                                                                        |

| 0x26           | -    | AAL2_TACT_PTR | Active transmit BD pointer. Points to the AAL0 BD currently being processed b AAL2 microcode. The address of the current BD in the table is (AAL2_TACT_PTR * 4) + TBDBASE. AAL2_TACT_PTR field provides bits [14 29] of the offset; bits [30-31] are always 00. |

|                |      |               | Host should write TBASE to this field during initialization. This pointer is advanced by the AAL2 microcode.                                                                                                                                                    |

| 0x28           | -    | AAL2_TQ_BASE  | Pointer to the first TPD in the AAL2_Tx_Queue. The actual address of the firs TPD is [(AAL2_TQ_BASE * 4) + AAL2_TPD_BASE].                                                                                                                                      |

|                |      |               | AAL2_TPD_BASE is the base pointer to the TPD space and is defined in the AAL2 parameter area common to all AAL2 channels; see Section 1.7.1, "AAL Parameter RAM."                                                                                               |

|                |      |               | The AAL2_TQ_BASE field provides bits [14-29] of the word-aligned offset from AAL2_TPD_BASE; bits [30-31] are always 00.                                                                                                                                         |

|                |      |               | Host writes this field during initialization. AAL2 microcode does not modify this field.                                                                                                                                                                        |

| 0x2A           | -    | AAL2_TQ_PTR   | Pointer to the current TPD in the AAL2_Tx_Queue. This is the TPD that the AAL2 microcode is currently processing (or will process next) in AAL2_Tx_Queue.                                                                                                       |

|                |      |               | The address of the current TPD in the AAL2_Tx_Queue is (AAL2_TQ_PTR * 4 + AAL2_TPD_BASE.                                                                                                                                                                        |

|                |      |               | AAL2_TQ_PTR field provides bits [14-29] of the offset; bits [30-31] are always 00.                                                                                                                                                                              |

|                |      |               | Host should write AAL2_TQ_BASE to this field during initialization. AAL2 microcode advances this pointer during normal operation.                                                                                                                               |

| 0x2C           | -    | CHEAD         | Channel header. This field contains the full (4 bytes) AAL0 buffer header of thi channel. AAL2 microcode appends the CHEAD field to the CPS-PDU to creat a complete AAL0 buffer. The byte ordering of this field is big endian.                                 |

|                |      |               | Host writes this field during initialization. AAL2 microcode does not modify thi field.                                                                                                                                                                         |

| 0x30 -<br>0x3E | -    | _             | Reserved, should be cleared.                                                                                                                                                                                                                                    |

#### 1.4.4 Example of AAL2 Transmit

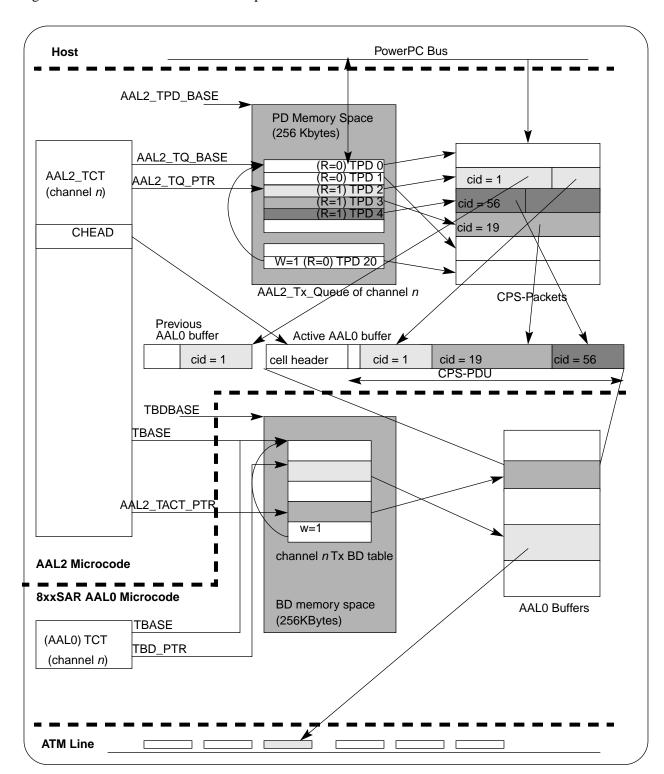

Figure 1-4 shows how CPS-Packets are packed into AAL0 buffers.

Figure 1-4. Example of the Transmit Data Flow of an AAL2 Channel

A description of the data flow shown in Figure 1-4 is as follows:

- The first part of the CPS-Packet (CID=1) has already been packed into the previous AAL0 buffer.

- The tail of CPS-Packet (CID=1) is packed into the active AAL0 buffer of this channel. TPD 2 is marked available (R=0).

- CPS-Packet (CID=19) is copied to the AAL0 buffer pointed to by TPD 3. TPD 3 is marked available.

- Only the first part of CPS-Packet (CID=56) has room in the active AAL0 buffer. The rest of the CPS-Packet remains in external memory to be placed in the next AAL0 buffer when the AAL2 microcode is activated again for this channel.

- The TxBD (pointed to by AAL2\_TACT\_PTR) that points to the active buffer is closed (R bit is set). (The 8xxSAR transmits this buffer later according to the APC or host scheduling.)

- Note that while the AAL2 microcode fills the active AAL0 buffer, the 8xxSAR (AAL0 microcode) uses TBD PTR to actually transmit the AAL0 buffers prepared earlier.

#### 1.4.5 Built-in Timer CU Support

The Timer CU mechanism is designed to guarantee a minimum packet throughput for an AAL2 channel. It ensures that transmit CPS-Packets are not delayed by the AAL2 microcode beyond the quality of service requirements for a channel.

In AAL2 operation, if a channel does not have enough CPS-Packets to fill a partially filled active buffer, the AAL2 microcode waits to send the buffer. If the active buffer is not filled with new CPS-Packets the next time this channel is activated, the microcode still delays sending the buffer in hopes of achieving a better utilization of the transmission line. The Timer CU mechanism limits this delay.

The AAL2 microcode implements the Timer CU mechanism using a wait table (AAL2\_TxWait\_table allocated by the host) and the CP's internal RISC timer software table. The wait table holds the remaining wait time for all partially filled active buffers. Each "tick" of the RISC timer activates the AAL2 microcode to pad (fill with zeros) and send all partially filled buffers which have expired. The duration between ticks is defined in the TIMEP field of the RISC controller configuration register (RCCR). The RISC timers are enabled in RCCR[TIME]. See the discussion of the RISC timer table and the RCCR in the communications processor chapter of the MPC860 User's Manual.

For each AAL2 channel using the Timer CU mechanism, the host should set AAL2\_TCT[ET] and initialize AAL2\_TCT[TCU]. Once initialized, the Timer CU mechanism does not require host intervention.

#### 1.4.5.1 Algorithm Description

This section describes the algorithm used to implement the Timer CU mechanism for timer-enabled channels.

#### 1.4.5.1.1 Starting the Timer for a Partially Filled Active Buffer

When the AAL2 microcode is unable to fill a channel's active buffer, it does the following:

• Starts the count down for the channel's partially filled active buffer by setting the AAL2\_TxWait\_table[X,Y] bit, where:

$X = (TCU + AAL2\_TxWait\_PTR)$  modulo (the number of rows in the wait table)

Y = channel number.

• Stores X in the channel's AAL2\_TCT (so that it can later clear the bit once the active buffer is sent, either full or partially filled).

The TCU field is defined in AAL2\_TCT of each channel. The wait pointer (AAL2\_TxWait\_PTR) is defined in the AAL2 parameter RAM area; see Section 1.7.1, "AAL2 Parameter RAM."

#### 1.4.5.1.2 Count Down Mechanism and Detection of Expired Buffers

Each advance of the wait pointer through the rows of the wait table corresponds to one RISC timer tick. The wait pointer marks the current row in the wait table. All bits that are set in the current row represent expired channels. Each time the RISC timer expires, it asserts a request to the CPM. This request in turn activates the AAL2 microcode to do the following:

- For each bit set in the current row, the AAL2 microcode:

- Pads the partially filled active buffer with zeros.

- Closes its BD (R=1). (The cell is sent the next time the channel is scheduled by the APC or the host issues an APC BYPASS command for the channel.)

- Clears the channel's bit in the wait table.

- The wait pointer advances to the next row of the wait table, thereby decreasing the wait time of all remaining partially filled active buffers by one RISC timer tick.

When the wait pointer reaches the end of the table, it advances back to the beginning. The size of the wait table is limited to 256 rows, which means that the maximum delay of an active buffer is (255 \* RISC timer period).

Note that if all the bits in the current row are 0 (which may happen in most cases), the AAL2 microcode simply advances the wait pointer. All channels in the wait table then become one row closer to the wait pointer, which means that one RISC timer period is subtracted from the wait time of all the partially filled active buffers.

The host controls the count down mechanism in each channel's AAL2 TCT:

- AAL2\_TCT[ET] defines whether the Timer CU mechanism for this channel is enabled.

- AAL2\_TCT[TCU] determines the maximum delay for the channel's partially filled active buffer (TCU \* RISC timer period).

For example, assuming the following:

- RISC timer expires every 0.5 ms,

- TCU = 6 (for channel n), and

- AAL2\_TxWait\_PTR points to row 3,

then, if the active buffer for channel *n* is only partially filled, the AAL2 microcode sets the *n*th bit in the 9th row of the wait table (6 rows from the position of the wait pointer).

#### 1.4.5.2 Example of Timer CU Implementation

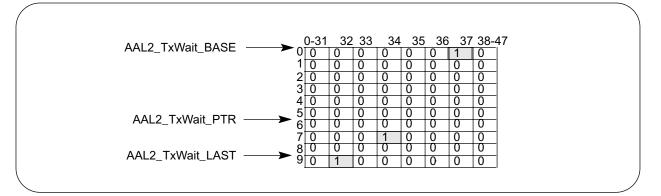

In Figure 1-5, the wait table is implemented with 10 rows. There are six AAL2 channels (channels 32-37). The width of the wait table is three half-word (48 bits). Columns 0-31, 38-47 of the wait table are unused (must be cleared by the host during initialization). The table width is programmable in 16-bit increments.

Figure 1-5. Example of the Wait Table

The wait pointer points to row 6. Channels 32, 34 and 37 have partially filled active buffers:

- Channel 34 expires in one RISC timer period

- Channel 32 expires in three RISC timer periods

- Channel 37 expires in four RISC timer periods

Note that if the partially filled active buffer is filled before its time expires, the AAL2 microcode clears the channel's bit in the wait table.

#### 1.4.6 Optional APC Overrun (APCO) Event Mask

When the user oversubscribes a channel, APC overrun events are generated by the CP. The AAL2 microcode provides the option to mask these interrupts by programming trap register four (RCTR4) as shown in Table 1-4.

Table 1-4. RCTR4 Initialization for APCO Masking

| Trap Register | 850SAR Rev. A and B | 860P and 855T |

|---------------|---------------------|---------------|

| RCTR4         | 0x933D              | 0x933F        |

The APC overrun mask bit (APCOM) is located in two previously reserved entries of the APC parameter table, as shown in Table 1-5.

Table 1-5. APC Parameter Table Additions for APCO Masking

| Offset         | Name    | Width    | Description                                      | User Writes  |

|----------------|---------|----------|--------------------------------------------------|--------------|

| APC Par + 0x18 | APCLST1 | HalfWord | APC level status for the first priority service  | User defined |

| APC Par + 0x38 | APCLST2 | HalfWord | APC level status for the second priority service | User defined |

Table 1-6 describes the APCLST field.

Table 1-6. APCLST Description

| Name            | Description                                                                                                                                                                                             |               |       |        |        |       |       |      |       |       |      |       |        |    |    |    |    |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|--------|--------|-------|-------|------|-------|-------|------|-------|--------|----|----|----|----|

| APCLST <i>n</i> | APC stat                                                                                                                                                                                                | us (first and | secor | nd lev | el). C | ontai | ns th | e AP | C ove | errun | mask | ζ.    |        |    |    |    |    |

|                 | Bit                                                                                                                                                                                                     | 0             | 1     | 2      | 3      | 4     | 5     | 6    | 7     | 8     | 9    | 10    | 11     | 12 | 13 | 14 | 15 |

|                 | Field                                                                                                                                                                                                   | APCOM         |       | •      | •      |       |       |      |       | _     |      | •     | •      |    | •  | •  |    |

|                 | The APCOM bit is described below.  Bits Name Description  O APCOM APC scheduling table overrun event mask for this APC O APCO interrupts are enabled.  1 APCO interrupts are disabled.  1–15 — Reserved |               |       |        |        |       |       |      |       |       |      |       |        |    |    |    |    |

|                 |                                                                                                                                                                                                         |               |       |        |        |       |       |      |       |       |      | APC I | level. |    |    |    |    |

|                 |                                                                                                                                                                                                         |               |       |        |        |       |       |      |       |       |      |       |        |    |    |    |    |

|                 |                                                                                                                                                                                                         |               |       |        |        |       |       |      |       |       |      |       |        |    |    |    |    |

#### 1.5 AAL2 Microcode Data Structures for Receive

This section describes the AAL2 microcode's data structures used for receiving AAL2 packets.

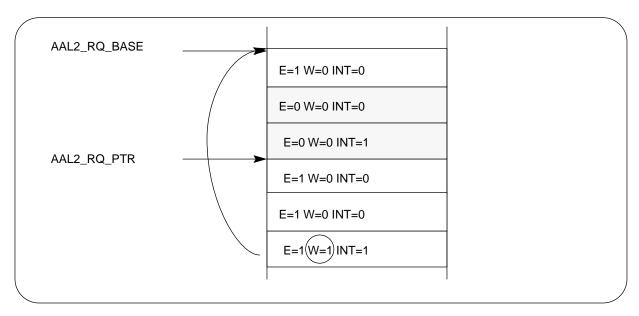

#### 1.5.1 Receive Packet Descriptor (RPD)

Similar to buffer descriptors, each receive packet descriptor (RPD), shown in Figure 1-6, contains control bits and the pointer to the CPS\_Packet. However, the RPD does not contain status bits. The status feedback from the CP is given through the exception queue; see Section 1.9, "AAL2 Microcode Exceptions." The host should program all RPD fields during initialization.

|            | 0 | 1      | 2 | 3   | 4 | 5 | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|------------|---|--------|---|-----|---|---|----|----|----|----|----|----|----|----|----|----|

| Offset + 0 | E | _      | W | INT | _ | _ | _  | СМ | _  | _  | _  |    |    | _  | _  | _  |

| Offset + 2 |   | _      | _ | _   | _ | _ | E0 | E1 | E2 | E3 | E4 |    | E6 | E7 | _  | _  |

| Offset + 4 |   | RP_PTR |   |     |   |   |    |    |    |    |    |    |    |    |    |    |

| Offset + 6 |   |        |   |     |   |   |    |    |    |    |    |    |    |    |    |    |

Figure 1-6. Receive Packet Descriptor (RPD)

Table 1-7 describes the RPD fields.

**Table 1-7. RPD Field Descriptions**

| Offset              | Bits | Name                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                     |  |

|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x00                | 0    | E                                                                                                                                       | Empty. Determines whether the CPS-Packet is accessible to the host or the AAL2 microcode.                                                                                                                                                                                                                                                                                                       |  |

|                     |      |                                                                                                                                         | 0 - The CPS-Packet associated with this RPD has been filled with the received packet or receiving has been aborted due to an error. Host is free to examine or to write to the fields of this RPD. The AAL2 microcode will not access this RPD while the E bit is 0. Host should set this bit after processing the CPS-Packet and RPD.                                                          |  |

|                     |      |                                                                                                                                         | 1 - The CPS-Packet associated with this RPD is empty, or is currently being filled by th AAL2 microcode. This RPD and its associated CPS-Packet can be used by the AAL2 microcode. Once the E bit is set, the host should not modify any fields of this RPD. AAL microcode clears this bit after it retrieves the CPS-Packet and updates the RPD.                                               |  |

|                     |      |                                                                                                                                         | During host initialization, E bit should be set in all RPDs.                                                                                                                                                                                                                                                                                                                                    |  |

| 0x00                | 1    | _                                                                                                                                       | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0x00                | 2    | w                                                                                                                                       | Wrap. Determines whether this is the last RPD in the AAL2_Rx_Queue.                                                                                                                                                                                                                                                                                                                             |  |

|                     |      |                                                                                                                                         | 0 - This is not the last RPD in the AAL2_Rx_Queue.                                                                                                                                                                                                                                                                                                                                              |  |

| this be             |      |                                                                                                                                         | 1 - This is the last RPD in the AAL2_Rx_Queue. After the CPS-Packet associated with this RPD is retrieved from the active AAL0 buffer, the AAL2 microcode returns to the beginning of the queue (using the RPD pointed to by AAL2_RQ_BASE). The number of RPDs in the queue is programmable and is determined only by the W bit and the 256 KBytes of memory allocated for the transmit queues. |  |

|                     |      |                                                                                                                                         | This bit is configured by the host during initialization and is not modified by the AAL2 microcode.                                                                                                                                                                                                                                                                                             |  |

| the AAL2 microcode. |      | Determines whether AAL2 interrupt is generated after this CPS-Packet is retrieved by the AAL2 microcode.                                |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     |      |                                                                                                                                         | 0 - No interrupt is generated after this CPS-Packet is filled.                                                                                                                                                                                                                                                                                                                                  |  |

|                     |      |                                                                                                                                         | 0 - No interrupt is generated after this CPS-Packet is filled.  1 - After the CPS-Packet is retrieved (and if AAL2_RCT[RPI] is set), the AAL2 microcode adds an entry to the exception queue with the AAL2 bit and RXB bit set. The global interrupt count (INT_CNT) is decremented. If the counter reaches zero, SCCE[GINT] or IDSR1[GINT] is set, and an interrupt is generated to the host.  |  |

|                     |      |                                                                                                                                         | This bit is configured by the host and is not modified by the AAL2 microcode.                                                                                                                                                                                                                                                                                                                   |  |

| 0x00                | 4-6  | <u> </u>                                                                                                                                | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0x00                | 7    | CM Continuous mode. Determines whether the CPS-Packet associated with marked as available to the host (E=0) after processing by the CP. |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     |      |                                                                                                                                         | 0 - Normal operation.                                                                                                                                                                                                                                                                                                                                                                           |  |

|                     |      |                                                                                                                                         | 1 - The E bit is not cleared after the RPD is closed, allowing the associated CPS-Packet to be automatically rewritten the next time the CP accesses this RPD.                                                                                                                                                                                                                                  |  |

|                     |      |                                                                                                                                         | Host writes this field during initialization. AAL2 microcode does not modify this field.                                                                                                                                                                                                                                                                                                        |  |

| 0x00                | 4-15 | _                                                                                                                                       | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0x02                | 0-5  | _                                                                                                                                       | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                    |  |

|                     |      | 1                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

**Table 1-7. RPD Field Descriptions (Continued)**

| should clear this bit after processing the RPD.  Host should clear this bit during initialization.  Indicates whether sequence number of the STF is valid.  O - Sequence number of the STF is valid.  1 - Sequence number of the STF is valid.  1 - Sequence number of the STF is valid.  1 - Sequence number of the STF is valid; if the OSF is less than 47, the AAL2 microcode begins processing at the octet pointed by the OSF (uses the next RPD in 1 queue), otherwise the complete CPS-PDU is discarded.  When this error is indicated, the CPS-Packet associated with this RPD is not valid. His should clear this bit during initialization.  Host should clear this bit during initialization.  Indicates whether the expected number of octets for a CPS-Packet overlapping into the CPS-PDU matches the STF.  O - The expected number of overlapping octets matches the STF.  The expected number of overlapping octets does not match the STF; if the OSF is less than 47, processing starts at the octet pointed to by the OSF.  When this error is indicated, the CPS-Packet associated with this RPD is not valid. Thost should clear this bit during initialization.  Ox02 9 E3 Indicates whether the OSF of the STF contains a value of 48 or greater;  O - OSF of the STF contains a value of 48 or greater; the complete CPS-PDU is discarded.  When this error is indicated, the CPS-Packet associated with this RPD is not valid. His should clear this bit during initialization.  Ox02 10 E4 Indicates whether a HEC error was detected in the CPS-Packet header.  O - No HEC error was detected.  1 - HEC error was detected.  1 - HEC error was detected.                                                                                                                                                                                        | Offset | Bits | Name | Description                                                                                                                                             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1 - Parity error was detected on STF field. The complete CPS-PDU is discarded. When this error is indicated, the CPS-Packet associated with this RPD is not valid. He should clear this bit after processing the RPD.    Not should clear this bit during initialization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x02   | 6    | E0   | Indicates parity error on STF field.                                                                                                                    |  |

| When this error is indicated, the CPS-Packet associated with this RPD is not valid. His should clear this bit after processing the RPD.  Host should clear this bit during initialization.  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |      |      | 0 - No parity error on STF field.                                                                                                                       |  |

| Should clear this bit after processing the RPD.   Host should clear this bit during initialization.   Ox02   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |      |      | 1 - Parity error was detected on STF field. The complete CPS-PDU is discarded.                                                                          |  |