# elftosb User's Guide

by: NXP Semiconductors

## 1 Overview

The elftosb tool creates a binary output file that contains the user's application image along with a series of bootloader commands. The output file is known as a "Secure Binary" or SB file for short. These files typically have a .sb extension. The tool uses an input command file to control the sequence of bootloader commands present in the output file. This command file is called a "boot descriptor file" or BD file for short.

The elftosb tool is command line driven and can be separately built to run on Windows OS, Linux OS, and Apple Mac OS. Currently, elftosb tool on Mac OS can only support non-secure boot images for i.MX devices because code signing tool (CST) is not supported on Mac OS. The MCU bootloader package contains the executable for all the three targets.

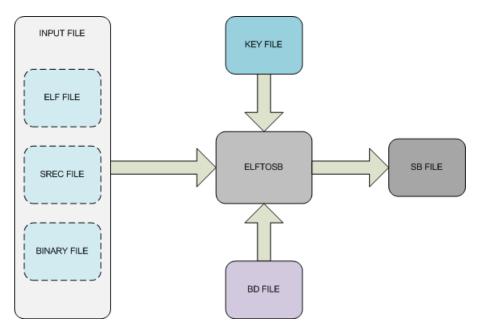

This document describes the usage of elftosb in terms of its command-line parameters, input command file (.bd) structure, and contents of the output (.sb) file. In the figure below, the block diagram describes the operation of elftosb at a high level. Elftosb utility uses the three inputs; Input file (elf/srec/binary), Key file, and BD file to process contents of the BD file in order to generate the output SB file.

## **Contents**

| 1 Overview 1                                       |

|----------------------------------------------------|

| 2 Command line interface2                          |

| 3 Command file 4                                   |

| 4 elftosb key file format 24                       |

| 5 Appendix A: Command file grammar24               |

| 6 Appendix B: SB boot image file format 28         |

| 7 Appendix C: SB2 boot image file generation 44    |

| 8 Appendix D: Master boot image file generation47  |

| 9 Appendix E: TrustZone-M preset file generation54 |

| 10 Revision history75                              |

Figure 1. elftosb diagram

# 2 Command line interface

The elftosb has a set of command-line options listed in the following table. Only the options that directly interface with what is described in the document are listed.

Table 1. Command-line options

| Option                            | Description                                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------|

| -p PATH,search-path PATH          | Adds a path to the end of the list of search paths                                               |

| -f CHIP,chip-family CHIP          | Selects output boot image format. For generating boot image for Kinetis device specify "kinetis" |

| -c FILE,command FILE              | Specify the command file to use. This option is mandatory                                        |

| -o FILE,output FILE               | Set the output file path. This option is mandatory                                               |

| -P VERS,product VERS              | Set product version                                                                              |

| -C VERS,component VERS            | Set component version                                                                            |

| -k FILE,key FILE                  | Add a key file and enable encryption                                                             |

| -z,zero-key                       | Add a key of all zeros and enable encryption                                                     |

| -D NAME=INT,define NAME=INT       | Override or set a constant value                                                                 |

| -O OPTION=VALUE,option NAME=VALUE | Set a global option value                                                                        |

| -V,verbose                        | Print detailed output                                                                            |

| -q,quiet                          | Print only warnings and errors                                                                   |

| -d,debug                          | Enable debug output                                                                              |

| -v,version                        | Display tool version and print list of supported device families                                 |

Table continues on the next page...

Table 1. Command-line options (continued)

| Option                          | Description                                                                                                                                                                                                           |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -?,help                         | Show usage information                                                                                                                                                                                                |

| -K/keygen <option></option>     | Generate AES-128 or AES-256 key file based on option value <128 256> (default <128>)                                                                                                                                  |

| -n/number <int></int>           | Number of keys to generate per file (default=1)(valid only when -K is specified)                                                                                                                                      |

| -x/extract/sbtool               | Extract a specified section                                                                                                                                                                                           |

| -i/index <int></int>            | Section index to extract (default=None Section) (valid only when -x is specified)                                                                                                                                     |

| -b/binary                       | Extract section data as binary. It is valid only when -x is specified. Warning: -q is enabled implicitly if -b is specified                                                                                           |

| -s/pkey <file></file>           | Path to private key for signing                                                                                                                                                                                       |

| -S/cert <file></file>           | Path to certificate files for signing. The first certificate will be the self signed root key certificate                                                                                                             |

| -R/root-key-cert <file></file>  | Path to root key certificate file(s) for verifying other certificates. Only 4 root key certificates are allowed, others are ignored. One of the certificates must match the first certificate passed with -S/cert arg |

| -h/hash-of-hashes <file></file> | Path to output hash of hashes of root keys. If argument is not provided then by default the tool creates hash.bin in the working directory                                                                            |

| -J/image-conf <file></file>     | Use this json image configuration file to produce master boot image (only for kinetisk3, k32w0x, lpc55xx and rt6xx family)                                                                                            |

| -T/tzm-conf <file></file>       | Use this json trust zone configuration file to produce trust zone binary configuration file (only for lpc55xx, and rt6xx family)                                                                                      |

The two command-line options required to set the command file and the output file paths are

- -c FILE, --command FILE

- -o FILE, --output FILE

These must be defined.

The -f or --chip-family option determines the format of the output (.sb) file elftosb utility will use. For generating boot image for Kinetis device specify "kinetis". The case is ignored when comparing chip family names.

The output boot image is not encrypted by default. To encrypt the boot image, provide one or more keys. Use the -z option to add a key that consists of all zeros. This is the default state of the hardware key in a chip if the key is not programmed yet.

One very useful option is -D or --define. This is used to set or override a constant value. The argument to the option is an identifier and an integer value separated by an equals sign. The constant name identifier can be any constant name allowed in the command files. The value can be any integer value allowed in the command files except for the multicharacter integer literals.

Before producing the output boot image, all constants set with the -D or --define options are set in the expression namespace inside the elftosb. These special constants override any constants with the same name that are specified in the command file. This enables the user to put a default value for a constant in the command file and override it with each invocation of elftosb.

Similar to -D is the -O or --option option that enables you to set or override the global option settings from the command line. The argument value is again an option name and the value is separated by an equals sign. The value can be any integer or string value allowed in the command file except for the multicharacter literals.

To extract the section content, use the -x/--extract/--sbtool option. Optionally, pass the index of the section required with the -i/-index option. The section indices are printed under the "Section table" header in the output. The -x option causes a hex dump of

the section contents to be printed inline with the output under the "Sections" header. If additional option -b/--binary is passed in

the command line, then the binary contents of the section are instead echoed to stdout enabling the user to easily redirect the

data to a file. In this mode, no other output is produced. In all cases, the section contents are decrypted before being displayed.

To generate a random AES-128 or AES-256 key file in the format described in Chapter 4, elftosb key file format, use the -K/--keygen <128|256> option.

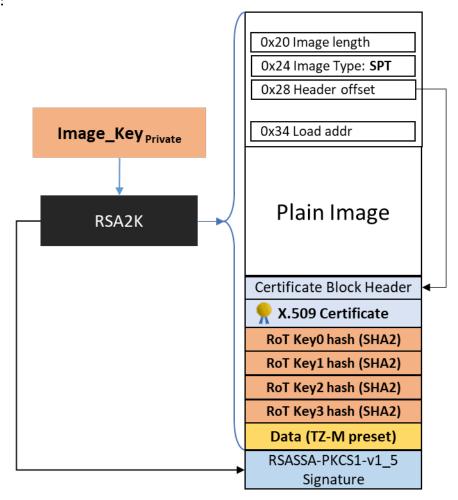

Switches -s/--pkey <file>, -S/--cert <file>, -R/--root-key-cert <file>, -h/--hash-of-hashes <file> are connected with SB2 file generation. The usage is described in Appendix C.

To generate master boot image for kinetis k3, k32w0x, lpc55xx, lpc55s1x, rt5xx, and rt6xx family use the -J/--image-conf <file> switch. More details can be found in Appendix D.

Creating of TrustZone-M preset binary configuration for lpc55xx, lpc55s1x, rt5xx, and rt6xx family use the -T/--tzm-conf <file> switch. Description of usage available in Appendix E.

The command-line usage for the elftosb tool is:

#### NOTE

- · There must be a space between the option (whether using short forms or long forms) and any value

- Any arguments listed after the options are the positional source files utilized by the extern() syntax (see Section 3.1.1.3, Sources).

### 3 Command file

The command files are text files in any encoding (including UTF-8) that use ASCII for the lower 128 characters. The line endings do not matter. Unix, DOS, and Mac OS endings are also supported. Even the mixed line endings are accepted.

The standard extension for the command (boot descriptor) files is .bd.

The elftosb command file functions like a linker command file. It describes the output ( .sb) file in terms of the input file(s). The elftosb command file supports the ELF, S-record, and binary input files. The command file can either explicitly declare the input files paths or can let the user provide the paths on the command line. This feature enables the command files to be generic and reusable.

The command file declares a number of source files and assigns unique and easily referenced names to each. Each source can either explicitly call out the path to its file or let the user provide the path on the command line. When a user enters a path in a command line, the path leads to a file which can change each time the elftosb is called.

The command file then defines the sections required in the output (.sb) file. Each of these sections provides a definition for a sequence of operations (such as load and call) that refer to the contents of the source files or constant values present in the command file. These operations are mapped to the bootloader commands.

### 3.1 Blocks

The command file consists of different blocks: options, constants, sources, keyblob, and sections. All blocks are optional and there can be more than one block of each type if required. The only rule is that all *Section* blocks must come after all other block types. The syntax of the block is shown below.

#### Example 1. Basic block syntax

```

# define the options block

options

{

# content goes here

}

```

### 3.1.1 Block syntax

Blocks are arranged in two groups within a command file. The first are the configuration blocks: options, constants, sources, and the keyblob. All configuration block types are optional, but at least one *sources* block is necessary for a useful command file.

The section definition blocks come after the configuration blocks. There can be more than one section block in a command file. Their lexical order in the command file determines the logical order of the sections in the output boot image.

### 3.1.1.1 Options

An *options* block contains zero or more name/value pairs and the option settings that assign values to global options used by the elftosb to control the generation of the output file.

Each entry in the options block takes the following form:

```

option_def ::= IDENT '=' const_expr

;

const_expr ::= bool_expr

| STRING_LITERAL

;;

```

Within the block, each option definition must end with a semicolon. The value of an option can be a string, integer, or boolean expression. The acceptable values depend on the particular option.

The option names are predefined by the elftosb utility and cannot be used in the command file for any other purpose. However, it is possible to have a source with the same name as one of the options. The complete list of available options is in the following table.

Table 2. Option names for elftosb

| Option name         | Applies to           | Description                                                                                                         |

|---------------------|----------------------|---------------------------------------------------------------------------------------------------------------------|

| alignment           | Section              | Power of 2 integer alignment requirement to start the boot image section                                            |

| cleartext           | Section              | Integer Boolean value. Makes a section unencrypted even in an encrypted image                                       |

| componentVersion    | Boot image           | Version string as "xxx.yyy.zzz"                                                                                     |

| driveTag            | Boot image           | Integer value that sets drive tag field of the image header                                                         |

| flags               | Boot image           | Integer value that is used for image-<br>wide flags                                                                 |

| productVersion      | Boot image           | Version string as "xxx.yyy.zzz"                                                                                     |

| secinfoClear        | GHS ELF source files | "default", "ignore", "rom", or "c" where "default" is equal to "c"                                                  |

| sectionFlags        | Section              | Integer value used to set flags for boot image sections or-ed with implicit flags                                   |

| toolset             | ELF source files     | "GHS", "GCC", or "ADS"                                                                                              |

| secureBinaryVersion | Boot image           | Used to specify version of SB2 file.<br>Expected values: "2.0", "2.1". If not<br>specified "2.0" is used as default |

The two version options is used to set the default product and component version numbers. Both the versions can be overridden from the command line.

The *flags* option sets the flags field in the header of a boot image file. See the appendix describing the boot image format for the possible values of this field. The same applies to the section *flags* option except that it sets the flags field in the boot image section header.

### 3.1.1.2 Constants

Similar to the options block, the constants block contains a sequence of zero or more constant definition statements which is followed by a semicolon. Each constant definition statement is simply a name/value assignment.

The constant definition syntax is shown below:

```

constant_def ::= IDENT '=' bool_expr

;

```

The constant values retain the integer word size when used in another expression.

The constant defined earlier in the constants block can be used in the definition of constants that follow it as shown in the following example.

### Example 2: Constants block

```

# this is an example constants block

constants {

ocram_start = 0;

ocram_size = 256K;

ocram_end = ocram_start + ocram_size -- 1;

}

```

### 3.1.1.3 Sources

The sources block is where the input files are listed and assigned the identifier which is referenced in the rest of the command file. Each statement in the sources block consists of an assignment operator (the "=" character) with the source name identifier on the left-hand side, and the source path value on the right-hand side. Each source definition ends with a semicolon.

The syntax for the source value depends on the type of the source definition. The two types are explicit paths and externally provided paths. The sources with explicit paths list the path to the file as a quoted string literal.

The external sources use an integer expression to select one of the positional parameters from the command line. It enables the user to change the input file by changing the command-line arguments.

The source definition syntax is as follows:

The source definition can also be a list of source attributes in parentheses at the end of the definition. These attributes are the same as the options in an options block. However, only a few options apply to the sources. See Table 2 for the complete list of options.

### 3.1.1.4 Keyblob

The keyblob blocks must be defined before section block types within a command file. A keyblob block must be referenced in a keywrap statement to be useful. The syntax for a keyblob block is shown below.

If the options list is empty, the corresponding keyblob entry is allocated but not populated. The supported keyblob option identifiers are:

- · start: The start address of the encrypted region

- · end: The end address of the encrypted region

- key: The AES-128 counter mode encrypted key for a region

- counter: The initial counter value for a region

- noByteSwap: Option used for data generation in elftosb based on used flash memory. 1 FLEX-SPI, 0 QUAD-SPI (default : 0)

#### **Keyblob Block**

#### NOTE

The region addresses that appear in the keyblob block must be supported by the underlying hardware. For example, an alias address may not be supported. See the corresponding chip reference manual for details.

### 3.1.1.5 Sections

The *section* blocks must be defined after the other block types within a command file. Each section block corresponds directly to a section created in the output (.sb) file. The syntax of *section* blocks has a section's unique identifier value and an option specific to that section. It is shown below.

The statement non-terminal is described in detail in Section 3.12, "Statements".

```

section_block ::= 'section' '(' int_const_expr section_options? ')' section_contents

;

section_options ::= ';' section_option_list

;

section_option_list

::= source_option ( ',' source_option )*

;

source_option ::= IDENT '=' const_expr

;

section_contents

::= '{' statement* '}'

| '<=' SOURCE_NAME ';'

;</pre>

```

As is demonstrated in the following example, there are two forms of section contents.

The first one contains a sequence of statements enclosed within braces. A bootable section can be created with a sequence of bootloader commands enclosed within braces. The syntax for statements in a bootable section are described in detail in Section 3.12, "Statements".

The second one creates an arbitrary data section. The raw binary contents of the listed source file are copied into that section of the output file. There is no predefined format or data sections. The data sections can be used to hold resource files or a backing store for virtual memory paging.

The output (.sb) file created for a MCU ROM must start with a bootable section. The ROM stops processing at the end of this bootable section. Additional bootable and data sections are ignored.

#### Example 4: Two section blocks

```

# create a bootable section

section (32)

```

```

{

# statements...

}

# create a data section

section (64) <= my_source_file;</pre>

```

The section identifier number that appears in the parentheses must be unique for that section. If two sections have the same identifier, an error is reported.

Set options that apply only to a single section by inserting them after the section's unique identifier separated by a semicolon. In the *sections* syntax above, options are described by the section\_options non-terminal. If there is more than one option then the options are separated by commas as in the *options* block.

Refer to Table 2 to check the options that apply to sections in output files.

#### alignment

This option takes an integer power of two as its value. The offset within the output (.sb) file to the first byte of a section with a special alignment is guaranteed to be divisible by the alignment value. Alignment equal to or below 16 is ignored as that is the minimum alignment guaranteed by the cipher block size of an output (.sb) file. Note, the section itself is aligned not the boot tag for that section. Any padding inserted to align a section consists of "nop" bootloader commands.

#### cleartext

Set this option to a boolean value. The keywords "yes", "no", "true", and "false" are accepted, as is any integer expression that evaluates to zero or non-zero. The default is false. If the output file is encrypted and the cleartext option is true, the section to which the cleartext option applies is left unencrypted. However, ROM does not currently support unencrypted bootable sections in an encrypted file. This option is most useful for data sections.

As with all options, these can be set globally using an options block instead of individually per section. The user can also set a global default and override it with a section-specific option. For example, set the default section alignment to 2 K and then align one particular section to 4 K.

Sections are always created in the output (.sb) file in the order they appear in the command file. In addition, the first bootable section that is defined in the command file becomes the section that the bootloader starts processing first after it reviews the output (.sb) file headers.

## 3.2 Lexical elements

This section describes the various textual components that go into a command file, their syntax, and how they are used. While reading the sections below, check the following table to understand the usage of token in the command file.

| Token            | Description                                                |

|------------------|------------------------------------------------------------|

| 10000            | Integer literal.                                           |

| 0x200            | Integer with value of 512.                                 |

| 256K             | Integer with value of 262144.                              |

| 0b001001         | Integer with value of 9.                                   |

| 'q'              | Byte-sized integer with value of 0x71 or 113.              |

| 'dude'           | Word-sized integer with value of 0x64756465 or 1685415013. |

| "this is a test" | String literal.                                            |

| \$.text          | Section name matching ".text".                             |

Table 3. Example token values

Table continues on the next page...

Table 3. Example token values (continued)

| Token             | Description                                                            |

|-------------------|------------------------------------------------------------------------|

| <b>\$</b> *       | Section name matching all sections.                                    |

| \$*.bss           | Another section name matching all .bss sections, such as ".sdram.bss". |

| appElfFile:main   | Symbol reference with explicit source file.                            |

| :printMessage     | Symbol reference using default source file.                            |

| {{ 01 02 03 0b }} | A four byte long binary object.                                        |

# 3.3 Whitespace

The whitespace in the form of space characters, tabs, newlines, or carriage returns are ignored throughout the command file except within a string. Any form of line ending is allowed.

# 3.4 Keywords

The following table lists every keyword used in the elftosb command files. These identifiers are not available for use as a source file or constant names. There are some of the keywords that are set aside for the features that are intended for the future and not in-use currently.

Table 4. Command file keywords

| call      | no       |

|-----------|----------|

| constants | options  |

| extern    | raw      |

| false     | section  |

| filters   | sources  |

| from      | switch   |

| jump      | true     |

| load      | yes      |

| mode      | if       |

| else      | defined  |

| info      | warning  |

| error     | sizeof   |

| qspi      | unsecure |

| ifr       | jump_sp  |

| enable    | keyblob  |

| start     | end      |

| key       | counter  |

Table continues on the next page ...

Table 4. Command file keywords (continued)

| keywrap | reset   |

|---------|---------|

| all     | encrypt |

### 3.5 Comments

The single-line comments can be introduced at any point in a line with a pound character ("#") or two slashes ("//") which runs until the end of the line.

The multi-line comments work the same as they do in ANSI C.

They begin with "/\*" and end with "\*/"

Additionally, as with ANSI C, there is no support for the nested multi-line comments.

### 3.6 Identifiers

The identifiers are used for the option names, constants, and source names. They follow the similar ANSI C rules for identifiers. They can begin with an underscore or alphabetic character and may contain any number of underscores and alphanumeric characters.

# 3.7 Integers

The integer literals are of one of these three supported bases: binary, decimal, or hexadecimal. The decimal integers have no prefix. The hexadecimal integers must be prefixed by '0x' and the binary integers must be prefixed by '0b'.

The integer literals can be followed by a metric multiplier character: "K", "M", or "G". The space characters are allowed between the last digit and the multiplier. Binary multiplier values instead of the standard metric multipliers are used. This means that "K" multiplies the integer by 1024, "M" by 1048576, and "G" by 1073741824. The lowercase "k", "m", or "g" are not allowed.

All integer values in a command file are unsigned and have a size associated with it. The supported integer sizes are byte (8 bits), half-word (16 bits), and word (32 bits). The integer literals are by default all word-sized values. To change the word size, the "word size" operator is used in an expression.

The integer constants can also be created with the character sequences contained in single quotes. One, two, or four character sequences are allowed. These correspond to byte, half-word, and word-sized integers. For example, 'oh' is equal to a half-word with the value of 0x6f68 hex (the value of the characters "o" and "h" in ASCII) or 28520 decimal.

Several keywords are set aside for the built-in integer constants for boolean values. These are "yes", "no", "true", and "false". The "yes" and "true" keywords evaluate to 1, while the "no" and "false" keywords evaluate to 0. These keywords can be used wherever the integer values are accepted including the command line.

### 3.7.1 Integer expressions

An integer expression can be used in any place where an integer constant value is required in an equation. These expressions (mostly) follow standard C expressions with a few exceptions. The following table lists the available operators.

Table 5. Integer expression operators

| Operator | Description |

|----------|-------------|

| +        | add         |

| -        | subtract    |

Table continues on the next page...

Table 5. Integer expression operators (continued)

| Operator | Description                      |

|----------|----------------------------------|

| *        | multiply                         |

| /        | divide                           |

| %        | modulus                          |

| &        | bitwise and                      |

|          | bitwise or                       |

| ۸        | bitwise xor                      |

| <<       | logical left shift               |

| >>       | logical right shift              |

|          | set integer size                 |

| sizeof() | get size of a constant or symbol |

In addition to the operators listed in the above table, the unary plus and minus are also supported.

### 3.7.1.1 Operator precedence

This table lists the expression operators grouped in their order of precedence. The first row in the table is the lowest and the last row is the highest precedence.

Table 6. Operator precedence in increasing order

| Operator  | Description                 |

|-----------|-----------------------------|

|           | bitwise or                  |

| Λ         | bitwise xor                 |

| &         | bitwise and                 |

| << >>     | left shift, right shift     |

| + -       | add, subtract               |

| * / %     | multiply, divide, modulus   |

|           | word size                   |

| unary + - | unary positive and negative |

### 3.7.1.2 Word size operator

The integer size operator (".") consists of a period followed by one of the characters "w", "h", or "b". These characters are case-sensitive. A whitespace is allowed between the period and the following character. This operator changes the word size for the expression to its left. The "w" character sets the size to a 32-bit word, "h" to a 16-bit word, and "b" to an 8-bit word.

For any given binary operation, the result is the largest word size of two operands. So, a byte-sized integer multiplied by a half-word-sized integer results in a half-word. The actual operation is always performed as 32-bit words and the result is truncated if necessary.

### 3.7.1.3 Sizeof operator

The size of operator is used to check the size of a symbol or a constant. The syntax of the operator is the keyword "size of followed by a symbol reference or constant identifier in parentheses (unlike in ANSI C). Sizes are always 32-bit values.

### 3.7.1.4 Constant references

Along with the integer literals, the expressions may refer to the constants defined in the constants' blocks by their name. A constant name is a standard identifier. Placing a constant name in an expression is equivalent to inserting that constant's integer value. Although the sources share the same namespace as the constants, they cannot be used within an integer expression.

## 3.7.1.5 Symbol references

Just like constants, the symbol references may also be used in integer expressions. A symbol reference has the value of the symbol's value in the ELF file and is a 32-bit value. Usually, a symbol's value is its address, although some special symbols can have other values. If the referenced symbol does not exist in the source file, then the symbol reference has a value of 0.

## 3.7.2 Boolean expressions

The boolean expressions are used while defining a constant, an option, or a condition for the if and else-if statements described in Section 3.12.6, "If-Else". The boolean expressions cannot be a source or target of a load statement.

| Operator         | Description               |

|------------------|---------------------------|

| &&               | boolean and               |

| II               | boolean or                |

| <                | less than                 |

| >                | greater than              |

| <=               | less than or equal to     |

| >=               | greater than or equal to  |

| ==               | equal to                  |

| !=               | not equal to              |

| exists(src_file) | does a source file exist? |

| defined(const)   | is a constant defined?    |

Table 7. Boolean expression operators

There is a number of new operators that can be used in the Boolean expressions. In addition to those operators, the unary not operator (or the character "!") is supported. All of these operators evaluate to either 0 or 1. Like in ANSI C, a value of 0 means false and any non-zero value means true.

There are two function-like operators that can be used in a Boolean expression. The first, "exists()", returns true if the source file named inside the parentheses exists on the disk and was opened successfully. It is a syntax error to put a source name that was not defined in a sources block inside an exists operator.

The second special operator is "defined()". It takes the name of a constant between the parentheses. The operator has a value of true if the named constant is assigned a value, either within the boot descriptor file or from the command line.

The && and || binary operators are short-circuit operators. This means that if the left-hand operand is equal to a value that makes the value of the right-hand operand not important (because the expression has the same end value either way), the right hand operand is not evaluated. This is particularly useful in expressions such as "if defined(const) && const > 10...". Here, the right-

hand greater-than expression is only evaluated if the constant "const" is defined. If the right-hand expression is always evaluated and "const" is not defined, an error is reported.

## 3.8 Strings

All string literals are contained within double quote characters. They may not extend beyond the end of a line. The C language backslashes used as escape sequences are not supported so that the backslash character can be used in the file paths. As a result it is not possible to insert a double quote, newline, or other special character in the middle of a string.

### 3.9 Section names

The named sections of the ELF files are selected with a section name literal. These special literals begin with a dollar-sign character ('\$') and continue until the first character that is not allowed in the section name. The name is a standard glob-type expression that can match any number of ELF sections. The acceptable characters include alphanumerics, underscore, period, asterisk, question mark, dashes, caret, and square brackets. Many of these characters are used only as a part of the glob expression.

The supported glob sub-expressions are:

| Expression | Description                                         |  |

|------------|-----------------------------------------------------|--|

| *          | Matches any character, zero or more times in a row. |  |

| ?          | Matches any single character.                       |  |

| [set]      | Matches any character in the set.                   |  |

| [^set]     | Matches any character not in the set.               |  |

In the list above, [set] is any combination of single characters and range. This range is formed using two characters separated by a hyphen: [a-z] inclusively matches all characters from "a" to "z".

When used in the section list of a load statement, a section name prefixed with a tilde ("~") character to invert the set of matched ELF sections.

## 3.10 Symbol references

The source files in the ELF format have a symbol table embedded in them. A symbol reference is used to refer to a particular symbol in an ELF file by its name. When used in an integer expression, the symbol reference has the symbol value which is its address.

The syntax for a symbol reference consists of an optional source file name followed by a colon and the symbol name. The symbol name is not placed in quotes and is used as a regular identifier.

If there is no source file before the colon, the symbol coming from the default source file that is specified with a "from" statement. If the symbol reference is not within the context of a "from" statement, the source file name is required.

### 3.11 Binary objects

The binary object values (known as "blobs") are a sequence of hexadecimal bytes that form an object. Double curly braces open and close a blob. Every two hexadecimal characters form one byte in the blob and all whitespace is ignored. The hex characters are case-insensitive. Non-hex characters are illegal and are not allowed within a blob.

### 3.12 Statements

Each statement within a bootable section block describes an "operation" that is performed by the bootloader when it processes the output (.sb) file. The individual statements correspond to at least one or more boot commands created in the output file. The elftosb interprets these statements and converts them into boot commands in the output file.

The sources block below has 3 statements. For all of the inline examples below, assume the following definitions:

```

sources

{

myElfFile = "app.elf";

mySRecFile = "utility.s37";

myBinFile = "data.bin";

}

```

This code above when in a boot descriptor file (.bd) is processed by the elftosb utility. The elftosb utility searches for app.elf, utility.s37, and data.bin files in the same folder and these files are then referenced as myElfFile, mySRecFile, and myBinFile in the output file.

All statements except the "from" and "if-else" statements must end with a semicolon.

### 3.12.1 Load

The load statement is used to store data into the memory. This load command includes the data loads, pattern fills, and word pokes commands used in the bootloader. The syntax of the statements can be simple but the interpretation can be very complex. In other words, a short load statement can produce a large sequence of boot commands and vice versa. The elftosb utility converts a load statement into bootloader commands.

The load command is also used to write to the flash memory. When loading to the flash memory, the region being loaded to must be erased before to the load operation. See the erase command for details.

An example code for a load statement is:

```

load_stmt ::= 'load' load_data ( '>' load_target )?

;

load_data ::= const_expr

| SOURCE_NAME

| section_list ( 'from' SOURCE_NAME )?

;

section_list ::= section_ref ( ',' section_ref )*

;

section_ref ::= ( '~' )? SECTION_NAME

;

load_target ::= '.'

| address_or_range

;

address_or_range

::= int_const_expr

| int_const_expr '..' int_const_expr

;

```

As shown in the code above, all load statements begin with the "load" keyword. Each load statement comprises of a data/ data source and a target location. The source is always required. The target can be implicit, in which case it is based on the source itself. Not all combinations of source and target types are allowed.

In the code above, the source is represented by the load\_data non-terminal. The source can be integer values, string literals, a source file, or one or more named sections of a source file. These sources result in one or more segments of data depending on the type of source. The data sources, and therefore segments, may or may not have a physical memory location associated with them. This memory location is the range of addresses in the memory where the data is placed by default.

#### Command file

For instance, a section of an ELF file is linked to a certain address and has a length. These combine to form the section's natural address and size. For example, the content of a binary file has a natural size but not an address.

The target of the load statement determines the address in memory where the source is loaded and also the length of the load. For certain source types that have a natural location, the target is optional and can be excluded from the statement. If listed, the target is placed after the source data and a '>' symbol. If the target is implicit, same as the source, a dot (period) after the '>' symbol is used. The value for the target is an address or an address range. When a target is a single address, it does not have a length associated with it. In this case, the length of the load comes from the source data itself. The references to symbols from an ELF file can also be used as a load target. They are equivalent to an address range, from the symbol's start address to its end address.

When the target is a single address, the entire data source is loaded to that address. This is true even if the source has a natural address. This allows the user to, for instance, load the ELF sections to different addresses from which they were linked.

When the target is an address range or a symbol equivalent to an address range, the source is both located and potentially truncated. The load address is the start of the target range. This works the same as with a single target address. If the natural size of the data source is equal to or smaller than the size of the target range (the end address minus the start address), then the entire source is loaded. The leftover bytes in the target are not modified in such cases. Whenever the natural size of the source is larger than the target range, the source is truncated to the size of the target address range when loaded.

The data sources that are composed of multiple segments, such as ELF files with multiple sections, must be loaded to their natural location. This is because only in target address only one address or range can be specified, and it is useless to load each segment to the same address.

The most common form of a load statement is loading a source file by name. This can produce quite different data sources depending on the source file type. The specific features of each data source type are described below.

**ELF file** — Using an entire ELF file as a data source causes all sections within the file to be loaded. Not all sections are loaded; only those sections whose type is SHT\_PROGBITS or SHT\_NOBITS are considered. All sections from the ELF files have natural locations and sizes.

```

# these two loads are completely equivalent

load myElfFile;

load myElfFile > .;

```

**S-record file** — The content of the file is turned into an in-memory image where contiguous regions of data are found by combining the individual load commands. The load segments are created from each of the contiguous regions. These segments do have natural addresses.

```

load mySRecFile;

```

**Binary file** — The entire content of the file forms one load segment that does not have a natural address. However, a binary file does have a natural length.

```

// load an entire binary file to an address

load myBinFile > 0x70000000;

// load part of a binary file

load myBinFile > 0x70000000..0x70001000;

```

**Binary object** — This is almost like a binary file except that the data is listed inline in the boot descriptor file. Again, raw binary data has no natural address but does have a natural length.

```

// load an eight byte blob

load {{ ff 2e 90 07 77 5f 1d 20 }} > 0xa0000000;

```

**ELF section list** – If user wants to load only certain sections of an ELF file, a syntax is supported that lets you select the ELF sections using glob expressions. See Section 3.9, Sections for information about the section names. The data source syntax is a list of one or more section names followed by the "from" keyword and a source name for an ELF file. The "from" keyword and

the following source name can be omitted if the load statement is within the "from" statement. The following examples demonstrate the syntax:

#### Example load block

```

// inclusive section name

load $.text from myElfFile;

// exclusive section name

load ~$.mytext from myElfFile;

// example load inside a from statement

from myElfFile

{

load $.text.*, ~$.text.sdram;

}

```

All sections of an ELF file have a natural location and size and the code in those sections expects to be at that location, an explicit load target must not be used. In fact, the elftosb utility allows only explicit targets for statements that select a single ELF section because it is not useful to load multiple sections to the same target address. On the other hand, it can be useful to relocate a single section to a new address in memory.

The actual comma-separated list of ELF section name expressions that follows the "load" keyword progressively filters the selected ELF sections. Each section name in the list if preceded by a tilde character ("~"), in which case the set of matched sections is inverted. For example, the section name "~\$.sdram.\*" matches every section that does not begin with ".sdram.".

In the above code block, check the third load command. The first section name "\$.text.\*" matches every ELF section that begins with ".text.". The second name (~.text.sdram) in the list matches every ELF section but the one named ".text.sdram" out of those sections matched by the previous section name. If the source file contains ".text.ocram", ".text.sdram", ".bss", and ".data" then only ".text.ocram" is selected.

**Integer value** — The integer value is a unique type of load data. This value is used as a pattern to fill a region of memory. The integer sources do not have a natural address but they do have a natural length.

```

# pattern fill

load 0x55.b > 0x2000..0x3000;

# load two bytes at an address

load 0x1122.h > 0xf00;

```

If you load an integer value to a single address, the load fills as many bytes as the integer value is long. The second load statement in the example above loads two bytes to 0xf00 because the integer value is a half word.

If you load an integer to an address range, only those bytes that are included in the range are filled. This is true even if the integer value size is larger than the address range length.

**String literal** — Using string literals as the load data source is very similar to loading a binary file. One use case of this is to fill a buffer in a memory that contains a message to be displayed to the user or printed over a serial port. When the buffer is set, user can invoke the print routine with a call statement.

```

# load a string at the address of a symbol

load "hello world!" > myElfFile:szMessage;

```

### 3.12.1.1 Load IFR

An IFR option to the load command that specifies that the data in the data source should be programmed to the Flash IFR index indicated in the target location.

The grammar is as follows:

```

load_ifr_stmt ::= 'load ifr' int_const_expr '>' int_const_expr

;

```

There are two forms of the load IFR statement, one to program to a 4-byte IFR location and another to program to an 8-byte IFR location.

#### 4-byte load IFR statement

```

section (0)

{

load ifr 0x1234567 > 0x30;

}

```

#### 8-byte load IFR statement

```

section (0)

{

load ifr {{11 22 33 44 55 66 77 88}} > 0x40;

}

```

### 3.12.2 Call

The call statement is used for inserting a bootloader command that executes a function from one of the files that are loaded into the memory. The type of function call is determined by the introductory keyword of the statement.

The grammar for these statements looks like this:

As with the load statement, the call statement begins with a special keyword. But, instead of a single keyword, there are two possibilities. The keyword selects which specific boot command is produced by the statement, depending on the output boot image format. In general, the "call" commands are expected to return the bootloader and the "jump" commands are not. For the boot images, "call" produces the ROM\_CALL\_CMD and "jump" produces the ROM\_JUMP\_CMD. See the boot image format design document for specific details about these commands, such as the function prototypes they expect.

After the introductory keyword comes the call target, of which there are three forms that have their own syntax. All forms of the target boil down to just an address in the memory. The different forms are described in detail below.

**Source file** — If a source file name is used as the call target, the call statement uses the entry point to that source file as the target address. This implies that the source file must have an entry point. If a source file that does not support entry points or does not have one set is used, an error is reported.

```

# call the entry point

call myElfFile;

# same here

jump mySRecFile;

```

19

```

# this produces an error because binary files

# do not have an entry point

call myBinFile;

```

**Integer expression** — Using an integer expression is the most straightforward call target. The expression simply evaluates to the address of the function that is invoked by the call or jump boot command.

```

# jump to a fixed address

jump 0xffff0000;

```

**Symbol** — Although it is just another form of integer expression, it is important to point out that a reference to a symbol in an ELF file can be used as the call target. Both the form where the source file is explicit and the form where it is implicit are supported. The implicit form uses the source file from the enclosing from statement. It is an error to use the implicit form outside of a from statement. It is also an error to list a symbol that is not present in the source file, or to use a source file with a type other than ELF.

```

# call a function by name and pass it an arg

call myElfFile:initSDRAM (32);

# this is the implicit form of symbol usage

from myElfFile

{

call :reboot();

}

# this is an error because Srecords do not have symbols

jump mySRecFile:anEntryPoint();

```

Note that the file the symbol comes from does not actually have to be loaded by the same command file. It is only used to find an address, whether or not the function actually exists at that location.

The final part of a call statement is the optional argument value. It is just an integer expression wrapped in parentheses. The expression determines what value is passed as the first argument to the call or jump boot commands. If the expression is excluded from the statement, then the argument value defaults to zero. Using empty parentheses is equivalent to completely excluding the parentheses.

### 3.12.3 From

More of a block than a true statement, the from statement has the simplest syntax. It produces no boot commands by itself. Instead, the from statement enables you to use simpler forms of the statements contained within it.

The simple grammar for the from statements follows this form:

```

from_stmt ::= 'from' SOURCE_NAME '{' statement* '}'

;

```

The from statement consists of the "from" keyword, a source identifier, and a sequence of statements enclosed in braces. There is no terminating semicolon after the closing brace. Any type of statement is allowed between the braces, except for the additional from statements, as they cannot be nested.

Certain forms of the load and call statements use an implicit source file. All the from statement does is setting this implicit source file for the statements found within it. This makes for cleaner and easier read command files.

#### The from statement

```

# name our input file

sources

{

```

```

example = extern(0);

# create a section

section (0)

{

from example

{

# load from example and call a function inside it

load $.ocram.*;

call :_start;

}

}

```

The above example demonstrates how the from statement is used. The load and call statements inside the from statement do not have any source explicitly listed. Which file should the named sections be loaded from? Which file is the "\_start" symbol located in? The from statement supplies the implicit source file for these statements.

The load statement loads all sections in the example source that have a name beginning with ".ocram.". The call statement generates a call boot command to the address of the "\_start" symbol within the example source file.

### 3.12.4 Erase

The erase statement inserts a bootloader command to erase the flash memory.

Grammar for the erase statement:

There are two forms of the erase statement. The simplest form (erase all) creates a command that erases the available flash memory. The actual effect of this command depends on the runtime settings of the bootloader and whether the bootloader resides in the flash, ROM, or RAM.

The second form of the erase statement accepts an address or address range as an argument. It erases the flash sectors that are intersected by the address or range. To erase a single sector, provide a single address within that sector.

#### The erase statement

```

sources

{

example = extern(0);

}

# create a section

section (0)

{

erase all;

load example;

}

```

### 3.12.5 Print

The print statement are actually three very similar statements that are used to print different categories of messages to the user. The three types of print statement are info, warning, and error. All print statements begin with a keyword corresponding to their type, as seen in the grammar here:

The info statement simply prints the message to the standard out. The message is visible unless the caller enabled the quiet output feature. The warning statement does basically the same thing as the info statement, except that it prefixes the message with "warning:". Additionally, the message is always visible. Finally, the error statement stops the execution of the elftosb immediately and prints the message prefixed by "error:".

#### The print statement

```

sources

# give the ELF file a name

afile = "file.elf";

constants

# create a constant that is the size of a symbol

bufsize = sizeof(afile: my buf);

# create a section

section (0)

if bufsize < 128

# elftosb stops after this is printed

error "Buffer size $ (bufsize) is too small!";

}

else

info "Buffer size $(bufsize) is acceptable";

/* ...more... */

}

```

The three print statements support the substitution of constant values and source file paths using a syntax like that for the Unix shell variable substitution. A constant name or source file name placed in parentheses and prefixed with a dollar sign causes the appropriate value to be inserted before the message is printed to the standard out.

For the constant substitution, there is a limited control of the formatting of the constant's value. The formatting options are placed before a colon that prefixes the name of the constant inside the parentheses. The two supported formatting options are the characters "d" and "x", only one of which is allowed at a time. The "d" character formats the constant as decimal and the "x" character formats it as hexadecimal. For example, "\$(x:floop)" formats the constant "floop" as hex.

### 3.12.6 If-Else

To make it easier to create reusable boot descriptor files, the elftosb has the if-else statement. These statements work just like the if statements in any other language you have used. Chain as many if-else statements as you like. The final else branch is optional and may be excluded.

The grammar looks like this:

```

if_stmt ::= 'if' bool_expr '{' statement* '}' else_stmt?

;

else_stmt ::= 'else' '{' statement* '}'

| 'else' if_stmt

;

```

There are several differences in syntax from the ANSI C. No parentheses are required around the boolean expression after the "if" keyword. Additionally, curly braces are always required around the statements on both the if and else branches.

All types of statements are allowed inside the if-else statement, including the from statements. The converse is also true: the if-else statements may be placed inside the from statements.

### 3.12.7 Erase QuadSPI all statement

The erase QuadSPI all statement erases the entire external QuadSPI flash.

The grammar is:

```

erase_qspi_stmt ::= 'erase' 'qspi' 'all' ;

```

#### Erase QuadSPI All statement

```

section (0)

{

erase unsecure all;

}

```

## 3.12.8 Erase Unsecure All statement

The erase unsecure all statement erases the entire internal flash, leaving the flash security disabled.

The grammar is:

```

unsecure_stmt ::= 'erase' 'unsecure' 'all'

;

```

#### Erase Unsecure All statement

```

section (0)

{

erase unsecure all;

}

```

### 3.12.9 Enable QuadSPI statement

The enable QuadSPI statement initializes the external QuadSPI flash using a parameter block previously loaded to the RAM.

#### The grammar is:

```

enable_stmt ::= 'enable' 'qspi' int_const_expr

;

```

#### **Enable QuadSPI statement**

```

section (0)

{

# Load quadspi config block bin file to RAM, use it to enable QSPI.

load myBinFile > 0x20001000;

enable qspi 0x20001000;

}

```

### 3.12.10 Reset statement

The reset statement generates a booloader reset command that resets the target device. Any additional commands in the SB file after the reset command are ignored by the bootloader.

The grammar is:

```

reset_stmt ::= 'reset'

;

```

#### Reset statement

```

section (0)

{

reset;

}

```

### 3.12.11 Jump with stack pointer statement

The jump with stack pointer statement generates a booloader jump command that sets the stack pointer before jumping. Any additional commands in the SB file after the jump command are ignored by the bootloader. The first argument is the value of the stack pointer. The second argument is the jump address. The third (optional) argument is the argument to the function being jumped to.

The grammar is below. The call\_target and call\_arg elements are described in the regular elftosb documentation.

```

jump_sp_stmt ::= 'jump_sp' sp_arg call_target call_arg?

;

sp_arg ::= int_const_expr

;

```

#### Jump with stack pointer statement

```

section (0)

{

jump_sp 0x20000e00 0x1000 (0x5a5a5a5a);

}

```

## 3.13 Common usage example

The most common use of elftosb is to simply load a single ELF file and jump to its entry point, which is almost always the \_start symbol defined by the C runtime library.

### Basic reusable boot descriptor file

```

// Define one input file that will be the first file listed

// on the command line. The file can be either an ELF file

// or an S-record file.

sources

{

inputFile = extern(0);

}

// create a section

section (0)

{

load inputFile; // load all sections

call inputFile; // jump to entry point

}

```

# 4 elftosb key file format

The key files provided to elftosb with the -k/--key command line switch have a very simple format. Each line of a key file contains one key which is an uninterrupted string of 32/64 hexadecimal characters, for a total of 128/256 bits of key data. Multiple keys may appear in a key file. Each key is on a separate line. The line-ending format is not significant.

#### Example 16. Key file with two 128 bits keys

```

3F3CFBC001F399991035C3C6C7065924

1BA3CD4030FC4376B4AA8CB5E932432E

```

#### Example 17. Key file with one 256 bits key

```

AAB5CCFB687D378C93821E8793337EA8F98B48A0B596F36CDD169347322E8C87

```

The contents of a key file are in plaintext.

# 5 Appendix A: Command file grammar

The grammar for the command file format is shown below in the Extended Backus-Naur Format (EBNF).

```

command_file ::= pre_section_block* section_def*

;

pre_section_block

:: options_block

| constants_block

| sources_block

;

options_block ::= 'options' '{' option_def* '}'

;

```

```

option def ::= IDENT '=' const expr ';'

;

constants block

::= 'constants' '{' constant def* '}'

constant def ::= IDENT '=' int const expr ';'

sources block ::= sources `{' source def* `}'

source def ::= IDENT '=' source value ( '(' source attr list? ')' )? ';'

source value ::= STRING LITERAL

| 'extern' '(' int const expr ')'

source attr list

::= option_def ( ',' option_def )*

section block ::= 'section' '(' int const expr section options? ')'

section contents

;

keyblob block ::= 'keyblob' '(' int const expr ')' keyblob contents

keyblob contents

::= '{' ( '(' keyblob options list ')' )* '}'

keyblob options list

::= keyblob option ( ',' keyblob option )*

keyblob_option ::= ( IDENT '=' const_expr )?

section options

::= ';' source attr list?

section contents

::= '{ ' statement* '}'

| '<=' SOURCE_NAME ';'

statement ::= basic stmt ';'

| from stmt

| if stmt

basic stmt ::= load stmt

| call stmt

| mode stmt

| message stmt

```

```

load stmt ::= 'load' load data ( '>' load target )?

load data ::= int const expr

| STRING LITERAL

| SOURCE NAME

| section list ( 'from' SOURCE NAME )?

section list ::= section ref ( ',' section ref )*

section ref ::= ( '~' )? SECTION NAME

load target ::= '.'

| address or range

address_or_range

::= int const expr

| int const expr \..' int const expr

symbol ref ::= SOURCE NAME? ':' IDENT

;

load_ifr_stmt ::= 'load ifr' int_const_expr '>' int_const_expr

call stmt ::= call type call target call arg?

call type ::= 'call'

| 'jump'

call target ::= SOURCE NAME

| symbol ref

| int_const_expr

call arg ::= '(' int const expr? ')'

jump_sp_stmt ::= 'jump_sp' sp_arg call_target call_arg?

sp arg ::= int const expr

from stmt ::= 'from' SOURCE NAME '{' in from stmt* '}'

in from stmt ::= basic stmt ';'

| if_stmt

mode stmt ::= 'mode' int const expr

```

26

```

message stmt ::= message type STRING LITERAL

message type ::= 'info'

| 'warning'

| 'error'

if stmt ::= 'if' bool expr '{' statement* '}' else stmt?

else_stmt ::= 'else' '{ ' statement* '}'

| 'else' if_stmt

encrypt stmt ::= 'encrypt' '(' int const expr ')' encrypt stmt list

encrypt stmt list

::= '{ ' ( statement ) * '}'

erase qspi stmt ::= 'erase' 'qspi' 'all'

unsecure stmt ::= 'erase' 'unsecure' 'all'

enable stmt ::= 'enable' 'qspi' int const expr

reset stmt ::= 'reset'

const expr ::= bool expr

| STRING LITERAL

int\_const\_expr ::= expr

bool expr ::= int const expr

| bool expr '<' bool expr

| bool expr '<=' bool_expr

| bool expr '>' bool expr

| bool expr '>=' bool expr

| bool expr '==' bool expr

| bool_expr '!=' bool_expr

| bool_expr '&&' bool_expr

| bool_expr '||' bool_expr

| '!' bool expr

| IDENT '(' SOURCE NAME ')'

| '(' bool expr ')'

| 'defined' '(' IDENT ')'

expr ::= INT LITERAL

| IDENT

```

```

| symbol ref

| expr '+' expr

| expr '-' expr

| expr '*' expr

| expr '/' expr

| expr '%' expr

| expr '<<' expr

| expr '>>' expr

| expr '&' expr

| expr '|' expr

| expr '^' expr

| unary expr

| expr '.' INT SIZE

| '(' expr ')'

| 'sizeof' '(' symbol ref ')'

| 'sizeof' '(' IDENT ')'

unary expr ::= '+' expr

| '-' expr

```

# 6 Appendix B: SB boot image file format

## 6.1 Glossary

AES-128 - Rijndael cipher with block and key sizes of 128 bits.

Block cipher - Encryption algorithm that works on blocks of N={64, 128, ...} bits.

CBC - Cipher Block Chaining, a cipher mode that uses the feedback between the ciphertext blocks.

CBC-MAC - A message authentication code computed with a block cipher.

Cipher block - The minimum amount of data on which a block cipher operates.

Ciphertext - Encrypted data.

DEK - Data encryption key, a one-time session key used to encrypt the bulk of the boot image.

ECB - Electronic Code Book, a cipher mode with no feedback between the ciphertext blocks.

Hash - Digest computation algorithm.

KEK - Key Encryption Key, used to encrypt a session key or DEK.

MAC - Message Authentication Code. Provides integrity and authentication checks.

Message digest - Unique value computed from the data using a hash algorithm. Provides only an integrity check (unless encrypted).

Plaintext - Unencrypted data.

Rijndael - Block cipher chosen by the US Government to replace DES. Pronounced "rain-dahl".

Session key - Encryption key generated at the time of encryption. Only ever used once.

SHA-1 - Hash algorithm that produces a 160-bit message digest.

### 6.2 Introduction

The entire boot image format is built around the requirements of AES-128, with its minimum block size of 128 bits or 16 bytes. AES-128 is the symmetric block cipher that is used for encrypted boot images. Using its block size as the base unit throughout the image makes it much easier to accommodate the encryption.

To support multiple executables within one image, the format has the concept of sections. Each section can contain a standalone bootable image, or may be a part of a larger sequence of sections. A boot command is provided that can be used to direct the bootloader to continue from another section at runtime.

There is a number of features of this format that are not useful for all applications or methods of reading. For instance, the section table is only useful if the random access to the boot image is available, while the boot tags are most useful when booting from a streaming media. The goal here is to provide a great deal of capability to the image, regardless of how it is accessed.

## 6.3 Basic types

Several basic C types are used throughout this document to represent cipher blocks, keys, and other important elements. The definitions for these types are shown below.

```

//! An AES-128 cipher block is 16 bytes.

typedef uint8_t cipher_block_t[16];

//! An AES-128 key is 128 bits, or 16 bytes.

typedef uint8_t aes128_key_t[16];

//! A SHA-1 digest is 160 bits, or 20 bytes.

typedef uint8_t sha1_digest_t[20];

//! Unique identifier for a section.

typedef uint32_t section_id_t;

```

## 6.4 Boot image format

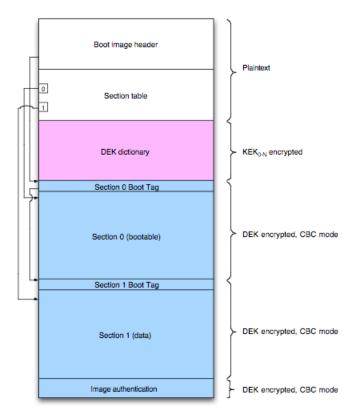

The boot image format consists of five distinct regions. First, there is a plaintext header containing basic information about the image. A section table, also plaintext, comes afterwards. It describes each of the different sections within the image. For encrypted images, a key dictionary that is used to support multiple customer keys then follows. Next, each section has its data, which is prefixed with a tag used by the bootloader. Finally, the image terminates with an authentication code for the entire image. The figure below shows the basic layout of a boot image.

The image format is designed to be read from the streaming media without the support for random access while requiring the caching of as little data as possible. However, the format also includes features that are most useful when the random access to the image is possible. For example, the image ends with an authentication code computed from the entire rest of the image. This isn't particularly useful for the ROM, but can be used by the host-resident utilities to verify and authenticate the boot images before using them.

Figure 2. Boot image regions

The basic unit size of the format is that of an AES-128 cipher block, or 16 bytes. Every region in the file always starts on a cipher block boundary. Every field within the image is formatted in the little endian byte order.

## 6.4.1 Image header

The header of a boot image is always unencrypted. It provides the required information about the image as a whole, as well as some useful pointers to the other regions within the image.

The image header size is always a round number of cipher blocks. Any padding bytes that are necessary to fill out the structure are always set to random values. No padding is necessary if the header completely fills the last cipher block it occupies. The section table dictionary immediately follows.

The C structure definition for the image header is:

**NXP Semiconductors**

elftosb User's Guide, Rev. 7, 02/2020

```

uint32_t m_firstBootTagBlock;

section_id_t m_firstBootableSectionID;

uint16_t m_keyCount;

uint16_t m_keyDictionaryBlock;

uint16_t m_headerBlocks;

uint16_t m_sectionCount;

uint16_t m_sectionHeaderSize;

uint8_t m_padding0[2];

uint8_t m_signature2[4];

uint64_t m_timestamp;

version_t m_productVersion;

version_t m_componentVersion;

uint16_t m_driveTag;

uint8_t m_padding1[6];

};

```

The fields of boot\_image\_header\_t have their descriptions in the following table. The flags defined for the  $m_flags$  field are shown in the second table.

Table 8. Image header fields

| Field                    | Description                                                                                                                                                   |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| m_digest                 | SHA-1 digest of all fields of the header prior to this one. The first 16 bytes (of 20 total) also act as the initialization vector for CBC-encrypted regions. |  |

| m_signature              | Always has the value 'STMP'.                                                                                                                                  |  |

| m_majorVersion           | Major version of the boot image format, currently 1.                                                                                                          |  |

| m_minorVersion           | Minor version of the boot image format, currently 1 or 2.                                                                                                     |  |

| m_flags                  | Flags associated with the entire image.                                                                                                                       |  |

| m_imageBlocks            | Size of the entire image in blocks.                                                                                                                           |  |

| m_firstBootTagBlock      | Offset from the start of file to the cipher block containing the first boot tag.                                                                              |  |

| m_firstBootableSectionID | Unique identifier of the section to start booting from.                                                                                                       |  |

| m_keyCount               | Number of entries in the DEK dictionary.                                                                                                                      |  |

| m_keyDictionaryBlock     | Starting block number, from the beginning of the image, for the DEK dictionary.                                                                               |  |

| m_headerBlocks           | Size of the entire image header in blocks.                                                                                                                    |  |

| m_sectionCount           | Number of sections.                                                                                                                                           |  |

| m_sectionHeaderSize      | Size in blocks of a section header.                                                                                                                           |  |

| m_padding0               | Two bytes of padding to align m_signature2 to a word boundary. Set to random values.                                                                          |  |

| m_signature2             | Always set to 'sgtl'. This second signature is only present in files with a minor version greater or equal to 1.                                              |  |

| m_timestamp              | Timestamp in microseconds size 1-1-2000 00:00 when the image was created.                                                                                     |  |

| m_productVersion         | Product version.                                                                                                                                              |  |

Table continues on the next page...

Table 8. Image header fields (continued)

| Field              | Description                                                                |  |

|--------------------|----------------------------------------------------------------------------|--|

| m_componentVersion | Component version.                                                         |  |

| m_driveTag         | Identifier for the disk drive or partition containing this image.          |  |

| m_padding1         | Eight bytes of padding to fill out the cipher block. Set to random values. |  |

#### Table 9. Boot image fields

| Constant             | Bit | Description                                                                                                                |

|----------------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| ROM_DISPLAY_PROGRESS | 0   | Turns on the progress reports of executed commands.                                                                        |

| ROM_VERBOSE_PROGRESS | 1   | Prints the extra information in reports about the executed commands. Applies only if ROM_DISPLAY_PROGRESS is also enabled. |

The m\_majorVersion and m\_minorVersion fields describe the version of the boot image format, not the version of the ROM (as in the previous boot image formats). The major version field is currently 1. Any time this field is changed, the format is no longer backwards compatible with the previous versions and a new bootloader is required. The minor version field should be incremented for any format changes that are backwards compatible with the previous bootloader versions. For instance, adding a new field to the end of the image header is backwards compatible due to the presence of the m\_headerBlocks field. In this case only m\_minorVersion should be incremented. However, if the image header fields are reordered, the current bootloader can no longer read the image and the m\_majorVersion field must be incremented. See the file format versions table at the end of this document for more version details.

If the value of the  $m_{keyCount}$  is zero, then the boot image is fully unencrypted. The image is always encrypted if there is at least one key in the dictionary.

The SHA-1 digest of the header provides a basic integrity check for unencrypted images. It does not provide any extra security because it can simply be updated along with any changes made to the header.